编辑丨青琰纪史

与双极器件比较,CMOS和BiCMOS器件的特点是产生的热量少。但当开关速率变快时,CMOS/BiCMOS器件的热耗散增高,例如一些高速CMOS/BiCMOS器件的热耗散已达到5W/芯片。

然而,常日空气冷却的陶瓷封装的热阻大于10℃/W,这就把硅芯片的热耗散限定在5W以下。由于常规的陶瓷封装的介电常数高,限定了这种器件的开关速率,以是高速CMOS/BiCMOS器件既须要有低的热阻又要有高的旗子暗记传播速率的一些新型封装。

AlN陶瓷

我们制备的A1N陶瓷的热导率和热膨胀系数。A1N陶瓷的导热系数大于200W/m·k,热膨胀系数与硅相似,这些特性都适用于高热导率和高可靠性的硅半导体器件封装。通过添加适当比例的烧结助熔剂和选用适当的烧结规范也可以达到上述特性。

1.腔体向下构造

插脚阵列式封装按其构造分成两种紧张类型:一种是腔体向上构造,另一种是腔体向下构造。如果考虑其本钱最好采取第一种构造,而第二种是降落热阻的最精品造。这种范例构造的剖视图及其热通道。

在腔体向上构造中(a),硅芯片中产生的热流经与硅表面平行的衬底,然后,热从盖帽边缘垂直传导到空气冷却的散热片中。

其余,在腔体向下构造中(b),热流直接通过衬底传导到大流量的散热片中,腔体向下构造的热通道长度较短,其宽度比腔体向上的宽,以是,腔体向下构造可用来降落热阻。研究者总是不选用腔体向下构造。

例如:Iwase等人12.宁肯采取A1N来降落热阻,也不选用腔体向下构造。当印刷电路板上的封装密度很低,而且通过印刷电路板的热流又相称大时,腔体向上构培养很实用。

但是,对付封装密度越来越高的印刷电路板来说,我们认为,最好不采取对印刷电路板影响较大的腔体向上构造,而是选择腔体向下构造。

2.聚酰亚胺内布线

用下列方程式表示旗子暗记传播延迟韶光“Ta”和传播间隔“L”的关系:Ta=√E₁·L/C(1)

式中c和C分别表示相对介电常数和光速。旗子暗记线的长度越短,周围介质的介电常数越小,旗子暗记传播得越快。半导体封装的紧张介质,AIN陶瓷与树脂比较,介电常数相称高。

由于与衬底表面平行的旗子暗记线很长,周围介质的介电常数起主导浸染,需在介电常数低的介质材料之间布线(例如:聚酰亚胺内布线)。此外,与衬底表面垂直的旗子暗记线短,以是可以在介电常数相称高的介质材料之间布线(如共烧钨互联通道)。

3.推举的构造

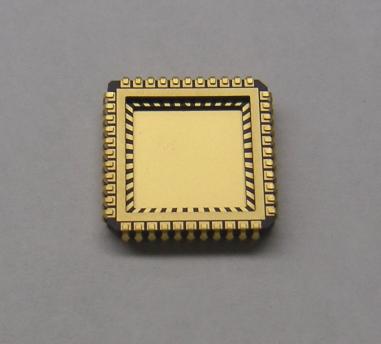

我们推举和试制的PGA(插脚阵列式)封装的剖视图,PGA封装的紧张零件是薄膜布线衬底和封装衬底,该构造的特性由下面给出。

(1)全A1N构造

高速高集成器件的耗散功率相称高,它们对污染也很敏感,以是必须从表面密封。因此AIN陶瓷可用来制作密封构造,同时也降落了热阻。

此外,高速高集成器件的焊点很多,因而封装尺寸可能变大,热膨胀失落配将引起一系列可靠性方面的问题。以是我们选择了全A1N构造,它的热膨胀系数与硅的附近。

(2)腔体向下

正如我们前面所述,腔体向下构造的封装常日比腔体向上构造的封装的热阻小,以是我们选择腔体向下构造。在某些情形下,焊点特殊多的芯片可能须要二维焊点定位和表面向下安装的设备(如CCB)。

但是,险些所有的从低本钱到高特性的芯片都用铝丝键合,以是我们打算设计一种适宜于引线键合芯片的封装,因此,在薄膜布线衬底和封装衬底之间采取小焊球,以便把旗子暗记运送到管脚。

为了减小传播延迟,用介电常数低的聚酰亚胺包封与衬底表面平行的旗子暗记线。通过AIN衬底的旗子暗记线的长度必须很短。我们选择最短的通道,即与表面垂直的直通道。焊环要防止受潮和其它外界造成的污染。

工艺

PGA封装的工艺流程。该工艺分3个紧张步骤,即薄膜布线的衬底工艺、封装衬底工艺和焊接工艺。图5示出了20mm高散热片的全A1N腔体向下PGA。

1.薄膜布线衬底工艺

采取抛光的A1N陶瓷板,表面粗糙度(R.)约为0.04μm;甩涂聚酰亚胺树脂然后进行固化,其厚度约为5μm;采取常日的光刻方法化学堕落掉聚酰亚胺层的中央区(芯片粘附区),以减少硅芯片到薄膜布线衬底之间的热阻。

同时去除聚酰亚胺层的边缘区部分(密封面),避免水气进入聚酰亚胺树脂层;淀积铝布线层,用光刻法化学刻蚀出所须要的图形,其厚度约为2μm;第二次涂覆聚酰亚胺,其厚度为3μm,然后固化并刻蚀出所需的图形;

淀积和离子铣Ti-Pt-Au多层焊层来制备管芯焊区,焊球连接区和密封区薄膜布线衬底;硅芯片常日是管芯键合和布线键合。

2.封装衬底工艺

A1N生瓷片冲制出互联通孔,把钨膏添补到通孔中;然后把这些带有互联孔的生瓷片重叠起来进行烧结。具有钨互联孔的抛光了的A1N陶瓷表面,钨和A1N稳定地烧结在一起,未创造A1N炸裂和其它问题;

对钨表面进行化学镀镍,把管脚钎焊到镀镍焊点的外边;把焊球放到镀镍焊点的里边,然后再流焊。封装衬底通过焊料球实现电连接。在封装边缘,用焊料环达到密封。

紧张特性

1.热阻

采取Vs.法(基极-发射极电压)丈量稳态热阻,丈量V。的目的是为了确定结温。一开始在低电流下测Vo,这样不至使结温升高,然后加大电流使结温升高,末了去掉加大电流,在结温低落之前,在低电流下丈量Vbt。

在空气冷却系统中,温度的韶光常数很长,以是加大的电流要持续10分钟。稳态热阻不仅要用电热仿照电路法丈量还要用此法进行打算。丈量和打算的热阻以及被测的样品构造。在腔体向下构造中,通过插脚传导到印刷电路板的热很少,以是我们简化了热通道。

在打算中,通过插脚的热通道忽略不计。实验证明:传到插脚的热由热绝缘体隔开。空气流速增大时,热阻降落;当空气速率为2m/s时,硅片到周围空气的热阻为2.7℃/W(散热片高20mm)。

2.电特性

用三维电感和电容仿照器“TRISIM-1”打算电特性。示出了其结果,电源线的自感为2.4nH,最长旗子暗记线的自感是20nH。从硅片键合点到插脚的最长旗子暗记线之间的电容为1.7pF。

3.氦检漏

对A1NPGA封装进行了氦检漏,结果表示种封装方案时,若只考虑管壳本身的本钱,每每使人误入歧途,因此,必须同时考虑IC的组装效率、二次组装及现场修理本钱以及利用新工艺的本钱。带引线的外壳每每是造成芯片焊接、引线键合、密封和测试时效率降落的根源。

管壳引线的破坏(哪怕只一条)导致电路的致命失落效,不可返修。从这一角度考虑,无引线芯片载体具有突出优点。特殊值得把稳的是几种低本钱封装的发展与运用。三种低本钱封装本钱与生产量之间的关系。

陶瓷四边有引线封装(CERQUAD)工艺相称于陶瓷双列直插(CERDIP)工艺,在陶瓷类外壳中造价最低;预模塑芯片载体(pre-moldedPLCC)与后模塑型(post-moldedPLCC)均属SMT类低本钱芯片载体。

输入角度和端口对AWG 器件性能的影响剖析给出在不同角度入射时输入波导中的光场分布情形。可看出输入的角度越小,得到的光场分布越强,衍射的效率也越高。波导宽度的大小直接决定了波导中功率的分布,波导的宽度越小,输入平板波导中的峰值谱线宽度越宽,衍射效率越低,反之衍射效率越高。

但在器件的研制中,波导芯层的宽度必须担保个中传输的单一模式,不许可高阶模式的产生,波导芯层的宽度在4~6 μm 之间。 是衍射效率受输出波导端口值影响的变革情形。

由此可知,要想得到高度衍射效率必须使输出平板波导的端口尽可能大,而且波导的间距越大,衍射效率越低,透露的光功率越大。

越靠近中央输入旗子暗记的衍射损耗越小、功率越高而中央波长的衍射损耗最小,功率最高。反之,输入旗子暗记的波长越偏离中央波长,衍射效率越小。

阵列波导数量和端口对 AWG 器件性能的影响剖析要使制备的 AWG 器件具有更高的衍射效率和更低的损耗必须对输出光谱进行优化,若使输出主峰更加突出,则次级衍射峰更低。次级衍射峰越多,主峰携带的能量越小,器件的性能也越差。

器件的输出波谱相应受阵列波导数量影响的变革情形,阵列波导越少,主峰携带的能量越小,次级衍射峰的能量也越高。阵列波导数的增加对主峰携带的能量有决定性的影响,增加阵列波导的数量是得到好的 AWG波谱特性最大略的方法。

因此,阵列波导数的确定除了要考虑降落损耗,还要考虑器件的波谱相应。在得到同样带宽的情形下,得到的衍射峰越平坦,器件的性能越好。比拟剖析可创造,提高阵列波导数和增大波导端口都可提高器件的衍射效率。

波导入光的一侧如果做成锥形,能提高器件对光的网络,从而提高衍射效率,降落衍射损耗。 当波导宽度取锥形端口和阵列波导数量对输入衍射效率的影响6 μm 时,阵列波导数 2M + 1 = 91,波导端口宽度 wg= a = 6 μm,衍射效率 ηi = 22.5%。

如果把波导的吸收端口取的足够大,即 wg = d = 26.5 μm,与阵列波导间距相当时,对输入光的吸收效率会得到很大提高,在这种情形下,衍射效率 ηin可达到99.7%。

在不同输入端口情形下输出波导中的串扰分布情形,从中可知,波导芯层宽度越大,串扰越小,越靠近中央波导,串扰也越小。 因此,在担保单模传输的情形下,波导的端口越大则可得到越小的串扰损耗,每条输出信道中的串扰都降到-38 dB 以下。

作为攻关及预研项目正在研制44~124管脚无引线陶瓷芯片载体及72插脚、88插脚、132插脚陶瓷PGA等。多层陶瓷布线的微组装产品已有多项运用,MCM技能已在发展。

高密度封装技能研究仅是刚刚起步,尚需化大力气开拓品种,扩大数量,同时加强封装材料研究、CAD研究并建立高密度封装测试系统。

结语

提出并试制了一种新型构造的陶瓷插脚阵列式封装。当空气流速为2m/s时,硅片到周围空气的热阻为2.7℃/W(散热片高20mm)。最长旗子暗记线的自感为20nH,最长旗子暗记线之间的电容为1.7pF。当-55~150℃的热循环试验24周期后,氦漏速约为10-°atm·cc/s。

参考文献[1]孙国华,张信,武德珍等.高性能聚酰亚胺复合股料的研究进展[J].中国塑料,2021,35(09):147-155.DOI:10.19491/j.issn.1001-9278.2021.09.022.

[2]向红兵,陈蕾,胡祖明.聚酰亚胺纤维及其纺丝工艺研究进展[J].高分子通报,2011(01):40-50.DOI:10.14028/j.cnki.1003-3726.2011.01.007.