对消费者来说,这显然也是一个好。

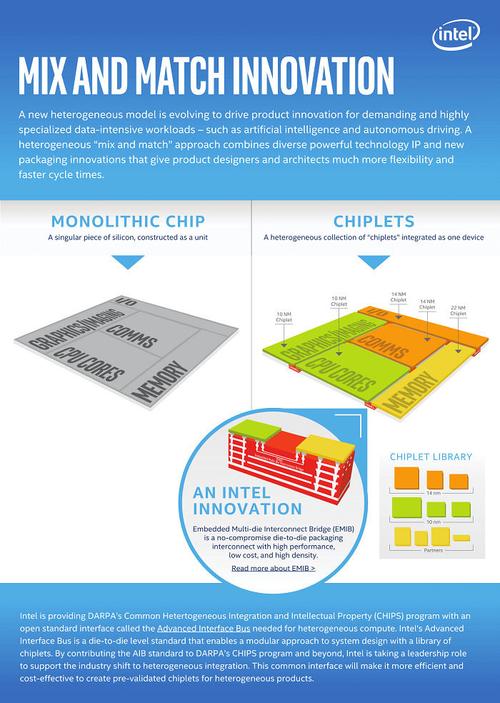

简而言之,该公司操持转向“小芯片、多硅片”,通过 EMIB 实现互联 ——将多个硅片组合到一起,拿出一副高度定制的芯片设计。

所谓‘芯库’(chiplet library),即预先设计的芯片元件(或 IP 块)的存储库,比如 I/O、存储器子系统、通信、CPU、GPU 等。

基于 DARPA 的通用异构集成和 IP 重用策略(CHIPS)中定义的单一封装,它们被设计为采取互联通用接口,性能亦靠近于单片设计。

其想法是可以将不同的硅片(稠浊匹配)组合到一起 —— 乃至不须要在同一工厂生产、或基于相同的工艺节点打造 —— 让它们在一个通用的接口下进行通信。

Stratix 10 FPGA 设计中的 EMIB 互联

就此而言,英特尔正在捉住 Hot Chips 的机会,畅谈其最靠近的成功设计,并期望在行业内携手推进。

凭借 Kaby Lake-G 和 Stratix 10 设计赢来的技能和政策支持,英特尔乃至为高等接口总线(AIB)指定了专用规范、并将其提交给了 DARPA 。

显然,英特尔希望自家能够主导 CHIPS 设计的标准接口,并为其代工业务部门(Intel Custom Foundry)供应帮助,后者目前难以找到母公司之外的客户。

Kaby Lake-G 是第一款面向消费者、直接应用 EMIB 技能的芯片。

英特尔表示,自家工艺优于竞争对手的 2.5D 方案(资料图:via WCCF Tech)

其不须要硅通孔(TSV)构建连接,在简化了设计的同时、不影响封装的良率。在“Fab 经济学”中,这一点是极具吸引力的。

比较之下,只管竞争对手有替代方案 —— 比如台积电的 CoWoS 和 InFO —— 但它们初期本钱更高昂、且增加芯片组装的工艺步骤。

有趣的是,AMD 最近已经展示了自己的片上通信替代方案,并表示这统统都无关紧要。

这统统意味着,芯片行业正在积极转向高度定制、整合、异构的设计,有望带来更快的芯片发布节奏、更高的通用性、以及更低的制造本钱。

[编译自:TechSpot]