作为摩尔定律武断的追随者和践行者,英特尔现任CEO Pat Gelsinger不止一次公开流传宣传“我们”会连续做摩尔定律的守护者,摩尔定律活着并且活得很好(Moore’s Law Alive and Well)。哪怕是另一家半导体巨子Nvidia的CEO黄仁勋宣告摩尔定律已去世,作为原教旨主义者的基辛格也坚持站队他的老前辈戈登摩尔。

我们从看似不可能的“四年五节点”操持和稠浊架构的引入都不丢脸出,Pat Gelsinger对付践行摩尔定律并不但是口头上说说而已,而从Intel目前制程节点的进度来看,四年五节点的操持正在正常推进。

为了达到业界内普遍不看好的摩尔定律,Pat Gelsinger自然深谙老前辈的教导,早在1965年,摩尔在一篇论文张就指出:构建大型系统时,将其分解为单独封装并互连的较小功能可能更经济,这是摩尔从芯片封装技能的角度去考量芯片能耗比与经济比,而这次英特尔全新的Meteor Lake架构便是从这句话开始的。

从PCH封装技能可同时封装芯片组,到采取了量产2.5D封装技能EMIB(嵌入式多芯片互联桥接)的数据中央、做事器CPU Sapphire Rapids,再到即将推出的、采取了3D Foveros从而达到分离式模块化设计的Meteor Lake,英特尔的创新型封装技能在业界保持领先水准,为摩尔定律的延续供应了强有力的支持。

那么什么叫做“分离式模块化”架构呢?大略点来讲,便是将CPU中各个功能分区模块化,根据目标需求,再将不同的模块组合在一起,而每个模块中又有不同的功分区,将这些模块排列组合,就和拼接乐高那样,把须要东西放上去,给予设计非常大的灵巧性,想增加什么功能就增加什么功能,想增强什么功能就增强什么。这次MTL的目标为PC史上出色的高能效平台、加速人工智能遍及、以及全新的Intel 4工艺为CPU核心性能以及集成显卡的性能带来提升。

我们可以看到下图左侧,这是MTL架构的一张示意图,本代的MTL共拥有四个模块(Tile):

最上面的为图形模块Graphics Tile;

中间的为专门为低功耗表现所打造的SoC Tile,这是MTL中是最大的创新点,我们将重点解析这个模块;

左下角为掌握接口的IO Tile;

右下角为高性能打算的Compute Tile,P核和E核位于此。

理解了这四个模块,我来分别讲解一下这些模块有什么用,有什么创新,以及会对我们普通用户的利用带来什么影响。

二、巧思妙想的“低功耗岛”SoC TileSoC Tile中集成了诸多的功能,下图中间蓝色框内便是SoC Tile中集成的所有功能,这里来说几个关键点:LP E-Cores、Media媒体引擎,Display显示功能、以及IOC掌握模块。

LP E-Core看到这个E-Core,大家可能遐想到自12代酷睿开始稠浊架构中的E-Core,但实在不然,这次的MTL除了在Compute Tile中的高性能核心与高效能核心外,在SoC Tile中还集成了两个LP E-Core即Low Power E-Core,低功耗能效核,组成了大核心+小核心+超小核心的高能效3D稠浊架构,往后我们在打算MTL的核心数量时还要计入LPE核心,这点大家须要把稳。并且非常不能忽略的一点是,LP E-Core是位于SoC Tile的,而不是Compute Tile。

如此一来,在一些非常低负载的任务中,直接调用LP E-Core就可以完成,而这些卖力低负载任务的功能区也基本都设计进了SoC Tile,例如媒体引擎、掌握各种接口、Wifi等的IOC和非常主要的内存掌握器等等,他们之间由极低功耗、极低延迟的NOC总线进行连接,可以直接访问内存掌握器。这些低负载的任务根本不须要“惊扰”到Compute Tile,由LP E-Core就可以完成打算,这便是本代MTL做到低功耗与高能效比的底层思路——很多小任务之前都须要激活E核心或P核心来处理,MTL的架构改变使得这些任务都交给这两个迷你核心完成了,传统意义上的CPU核心都在睡大觉,功耗肯定就低了,这部分模块也被很形象的称为“Low Power Island”即“低功耗岛”。

LP E-Core可以讲是MTL架构的核心,也是SoC Tile的核心。

媒体引擎与显示引擎媒体引擎与显示引擎按照我们的思维老例,该当是处于GPU中的,但MTL创新式的将这两部分功能加入进了SoC Tile中,这就带来了两个最直接的好处。

首先,看视频、视频通话等“视频”干系的功能,是大部分用户在利用条记本电脑时相称常用的功能,在之前,传统的CPU架构须要连通CPU核心、GPU核心再连接到内存掌握器,也便是说全体CPU险些都须要通电才能完成这个任务,例如下图所示,花费自然就比较大了。

而MTL便无需如此,媒体引擎和显示引擎被单独拿出来放到了SoC Tile中,而SoC Tile中又有着LP E-Core这种超低功耗核心,也便是说,在视频任务方面,只须要SoC Tile便可以消化完毕了,根本无需在图形处理模块Graphics Tile与打算模块Compute Tile中通电,大大降落了功耗,这是MTL非常有针对性的一大改变。

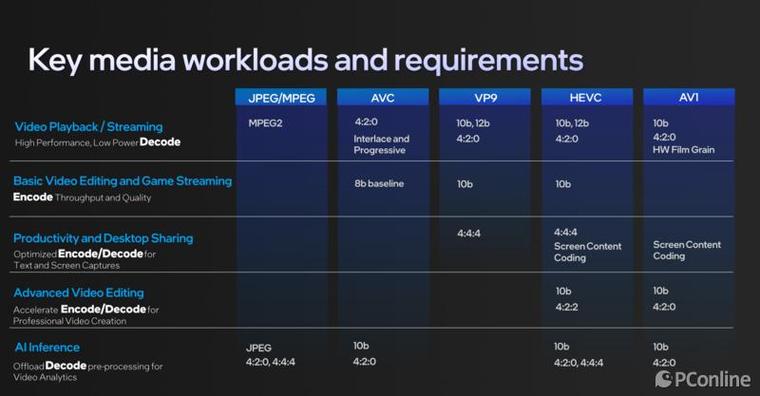

本次的媒体引擎依旧强大,尤其在编解码的硬件支持上还是保持着领先地位,例如:可以硬件层面编解码HEVC格式、10bit色深、4:2:2采样的视频,作为比拟,售价高达12999+的消费级顶端独立显卡Nvidia RTX 4090不支持该视频格式下的硬件编解码。其余在显示引擎方面,支持HDMI2.1、DP2.1,支持一个8K 60Hz HDR显示器或同时连接四个4K 60Hz HDR显示器。

与媒体引擎同理的还有IOC,Wi-Fi、蓝牙、USB、PCIe等等交由IOC统一调配后再交给LP E-Core处理。

人工智能专用引擎NPU当下,AI方面的运用可以讲是风光无限,英特尔自然不会错过这个机遇,除了传统的CPU和GPU外,英特尔MTL中还有专门用于AI打算的NPU引擎,为PC带来更强的AI能效,使得个人用户无需付出高昂的代价便可完成AI任务,加速遍及AI。

本次MTL中的NPU集成了两块神经打算引擎,由推理管道和可编程数字旗子暗记处理器组成,个中推理管道拥有更高效与灵巧的矩阵乘法和卷积,支持了FP精度下多种函数、量化网络的数据类型转化和领悟操作、输出数据的重新布局;每个神经打算引擎包含两个超长指令字数字旗子暗记处理器,为高吞吐量激活函数供应增强的浮点向量指令,支持lnt4到FP32数据类型。

此外还有DMA引擎和暂用内存,可将数据引入软件管理的SRAM,图形编辑器会优化调度DMA任务,支持前辈的数据重新布局。

对付目前常见的AI运用、大模型库例如Stable Diffusion,NPU都可供应强劲的性能支持,其余在能耗方面,NPU同样也设置在了SoC Tile中,这样一来,类似于背景虚化、人眼角度纠正等功能便可在SoC Tile中完成了,提高了条记本电脑的续航能力。独立的NPU使得MTL在AI方面的整体能效提升了8倍。

三、Graphics Tile与Compute Tile——性能与能耗兼得

分离式模块化架构让MTL的设计可以“既要也要”了,SoC Tile看重能耗比方面,而Compute Tile和Graphics Tile则可以专注于性能提升。

对付Compute Tile和Graphics Tile,这次媒体会中Intel放出的信息并不多,我们目前已知的信息为Compute Tile中是首次基于Intel 4制程工艺的核心,性能核心为Redwood Cove微架构,能效核心为Crestmont微架构,旗舰型号可能为6个P核+8个E核+2个LPE核的规格。

Graphics Tile则会升级为全新的Xe LPG架构,自9代酷睿开始,到11代酷睿再到上代的Xe LP微架构集显,每次都有两倍的性能提升,Intel近几年又在独立显卡方面汲取了大量的履历与技能积累,本次的Xe LPG便是在Arc独立显卡的Xe HPG微架构改进而来,性能会比当前的Xe LP微架构提升较多。

由于将媒体引擎和显示引擎移至了SoC Tile中,以是Graphics Tile理论上许可堆料的空间更大了,本次的MTL的集显将最高拥有8个Xe核心,也便是128EU,比较于Xe LP期间的96EU,规模提升了,架构也提升了。同时,本次MTL中集显还支持DX 12 Ultimate,拥有8个光追单元,在性能、硬件支持方面将会迎来比较大的提升。

四、全新的Intel Thread Director 英特尔线程调度器线程调度是自12代酷睿引入大小核架构之后的“难题”了,任务是由E核心运行以担保能效,还是需由P核心运行来达到更好的性能表现,这便是大小核心架构下的线程调度问题。在12代酷睿初期,不仅仅是普通的用户在抱怨调度问题,很多软件的开拓者也常常抱怨软件在调度方面的的优化比较困难。

不过经由多次的迭代、软件的更新以及Win11系统的更新,目前的调度问题已经优化提升的非常不错了,而到了MTL之后,虽然是再次引入了全新的架构,但英特尔可能不会再犯12代酷睿时有些“赶鸭子上架”的缺点了,全新的英特尔硬件调度器整装待发。

Intel与微软互助,在Windows系统层级进行了优化,本次英特尔硬件调度器并不是直接把任务分配核心,而是加入了一层根据核心状态时时更新的“评分系统”,更加精准的为操作系统报告准确的能力评估,从而进行线程调度。那么这套系统是怎么做到的呢?

首先每个任务将分为4个等级,分别为Class 0~Class 4。

Class 0代表着P核心和E核心在实行这个任务时每时钟实行指令数量基本同等;

Class 1代表着P核心比E核心在实行这个任务时每时钟实行指令数量多;

Class 2代表着P核心比E核心在实行这个任务时每时钟实行指令数量明显多;

Class 3代表着E核心比P核心在实行这个任务时每时钟实行指令数量少。

在把任务分级之后,再根据每个核心当下的状态进行打分,选出最适宜实行这个任务的核心,Windows就会把这个任务分配给该核心运行。

即是说,英特尔线程调度器将会具备两个过程,一是任务评级,二是核心评分,双重保障精确的核心用于精确的任务,以达到更佳的性能状态,其余,这还有助于提升能效比,MTL能否达到更高的能效比,除了“低功耗岛”的效果外,英特尔线程调度器也是至关主要的一点。

五、写在末了全新的前辈封装办法,重塑了全体架构,让芯片的设计更加灵巧,使得Meteor Lake可以达到在性能和功耗方面的“既要又要”,就像拼乐高一样,用户须要什么就往上面加什么。独特的低功耗岛可以看到英特尔架构师们的巧思妙想,短短两代产品之后我们又看到了全新的设计思路,为消费级CPU再次带来了变革。

LP E-core的加入,SoC Tile中的设计,独立的NPU,全新的Intel 4工艺,Meteor Lake奠定了这之后英特尔CPU的架构特点,加上英特尔在芯片领域多年的领先定位、重新夺回的制程上风以及对用户侧需求的深耕,Meteor Lake的实际表现将非常可期,连续支撑摩尔定律向前发展。

末了,在发布日期方面,根据刚刚结束的Intel Innovation,Pat Gelsinger宣告Meteor Lake处理器将于今年的12月14日正式发布,个人估量明年年初将会有搭载Meteor Lake处理器的终端产品开售。