图1 年出货量

摄影机自19世纪以来有着悠久的历史。第一台数码相机原型于1973年在贝尔实验室制造,它是基于一种名为电荷耦合器件(CCD)的图像传感器。后来,第一台商用数码相机——基于MOS传感器的Cromemco Cyclops于1975年问世。这台相机没有自己的永久存储器,必须连接到打算性能力查看图像。图2显示了Cyclops拍摄的32x32像素的图像。

图2 Cromemco Cyclops 拍摄的图像

目前大多数智好手机摄像头都是基于CMOS图像传感器(CIS)技能。自1993年喷气推进实验室发明以来,这些行业开始在智好手机摄像头上采取CIS技能。从那时起,由于CIS制造工艺的发展,智好手机图片的图像质量大大提高。这一点从图3中看出,图3显示了十多年前iPhone(带CIS)拍摄的图像。图片质量的提高以iPhone 4(2010)和iPhone 3GS(2009)以最小亮度拍摄的黄色框为标志。CIS的最新进展可以从iPhone 14(2022)拍摄的照片中看到,这张照片是在阴郁的天空中拍摄的,如图4所示。从图3和图4的图像比拟中不丢脸出,CIS的增长及其在智好手机行业的贡献显而易见。

图3 2009年iPhone3GS(左)和2004年iPhone4(右)拍摄的图像

图4 2022年iPhone14拍摄的图像

A.CIS的事情事理

图像传感器是检测光子并将其转换为电旗子暗记的半导体器件,这些电旗子暗记经处理后可以转换为故意义的图像。光电二极管捕获光子并将其转换为电子,然后将电子转换为电压。利用模数转换器(ADC)将该仿照信息转换为数字信息,并进一步处理以得到终极图像。只管CIS是当今广泛利用的图像传感技能,但其基本事情事理来源于其前身电荷耦合器件CCD。

CCD和CIS事情事理的比较如图5所示。CCD和CIS都由像素阵列组成。每个像素由CCD中的光电二极管和电极以及CIS中的光电二极体和晶体管组成。在CCD中,当光子撞击光电二极管时,它们被转换为电子,然后电子从一个像素转移到另一个像素,末了转移到寄存器,在那里它们被转换成电压并放大。与CCD相反,在CIS像素中,在像素本身中得到电压信息,随后,利用来自所有像素的垂直或水平条同时读取电压。一些CIS在芯片本身上具有ADC,并且传感器的输出已经被数字化。由于CIS中的信息读出速率更快,信息丢失最小,功耗低,因此在过去的十年中,它们已经取代了CCD。

图5 CCD和CIS的事情事理

B.CIS的演化

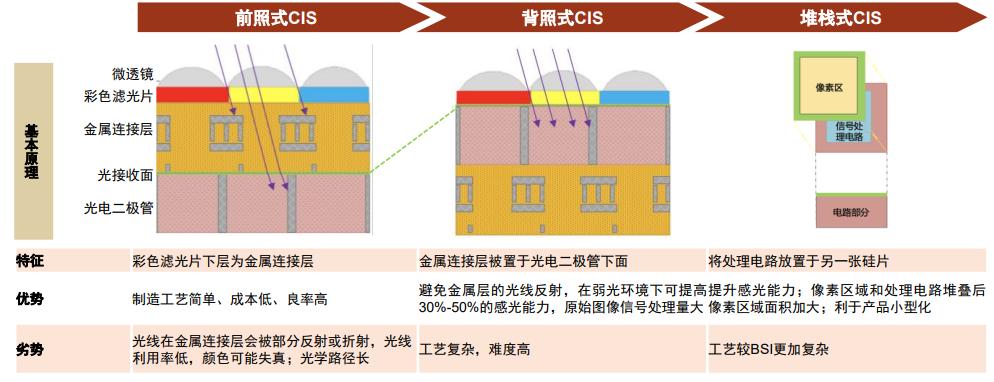

自1993年发明以来,当今市场上可用的CMOS图像传感器已经经由了几代的发展。传统的CIS是前照式的,其顶部有微透镜和滤色器,然后是用于互连的金属布线和位于架构底部的光电二极管。由于光通过金属层进入图像传感器,一些光旗子暗记在传输过程中乃至在到达光电二极管之前就被反射并丢失。显然,这种支配影响了前照式传感器的性能,当索尼公司提出将光电二极管移动到滤色器阁下的架构顶部时,这个问题得到理解决。这种构造被称为背照式(BI)CMOS图像传感器,它极大地提高了传感器的性能,从而标志着CMOS图像传感器新时期的开始。前照式和背照式的CMOS图像传感器的比较如图6所示。

图6 前照式和背照式的CMOS图像传感器的比较

继背照式传感器之后,学者们提出了堆叠像素和逻辑电方面的改进想法,以减小传感器在X和Y方向上的尺寸。图7显示了传统BI-CIS的三维视图(左),个中传感器的像素和逻辑电路共享同一基板和堆叠传感器(右),包含光电二极管的像素部分被放置在顶部,逻辑电路被移动到支撑基板上的架构的底部。这被称为堆叠背照CMOS图像传感器,由索尼公司于2012年提出。

图7 传统BI-CIS(左)与堆叠式BI-CIS

本文先容了业界进行的各种研究事情,并展示了堆叠背照CMOS图像传感器(BI-CIS)的一些改进。研究事情的重点是探索堆叠传感器的各种制造工艺,并改进光电二极管的不同性能指标。这些进步对CMOS图像传感器的发展至关主要,由于它们反过来又为智好手机行业做出了贡献。

2.利用硅通孔的堆叠BI-CIS(研究者:H. Tsugawa等, 2017)滚动快门失落真是智好手机和专业数码相机中常见的征象。当要拍摄的感兴趣工具以大于传感器速率的速率移动并且帧的底部比帧的顶部晚被捕获时,这种图像失落真就会发生。这种滞后会造成图像失落真,数码相机中的机器快门通过仅将传感器暴露于传感器可以处理的特定时间帧来战胜这个问题。但是,机器快门不能用于智好手机以减少图像失落真。探索减少智好手机CIS中图像失落真的研究是本文所谈论的研究事情背后的动机。

研究表明,CMOS传感器中的图像失落真是由传感器构造的输出接口处的低读取速率引起的。如图8所示,在传统的堆叠CIS中,来自像素层的图像信息通过DRAM层到达逻辑电路,并以串行办法离开输出接口(I/F)。纵然像素部分能够捕获全体图像,接口也只能串行地读出信息。与像素端比较,这导致I/F处的读取速率延迟,从而导致失落真。为了肃清失落真,添加一个临时存储器来存储像素信息彷佛是一个可行的办理方案。但是,这意味着像素大小正在增加,从而影响图像分辨率。

图8 不带DRAM(左)和带DRAM(右)的堆叠BI-CIS

通过改变图像传感器架构中的数据流而不是像素,能够改进I/F处的图像失落真。在逻辑层和I/F层之间添加了1Gbit DRAM存储器层,图9显示了3层像素/DRAM/逻辑配置。像素的输出通过DRAM到达逻辑层,然后来自逻辑层的数据暂时存储在DRAM层中,直到I/F准备好读取信息。须要把稳的是,在像素侧读取速率增加到120fps,而在I/F处读取速率保持在30fps,这与没有DRAM的情形相同。在像素输出处添加DRAM层和120fps的读取速率在很大程度上减少了终极图像中的滚动快门失落真效应。

图9 三层像素/DRAM/逻辑CIS的构造

A.利用硅通孔的堆叠BI-CIS的构造

图9中显示的3层堆叠CIS的构造利用两层堆叠的硅通孔(TSV),对像素利用90nm CMOS工艺,对DRAM利用30nm工艺,对逻辑层利用40nm工艺。中间DRAM和逻辑层通过下TSV堆叠连接,像素基板和下TSV堆栈通过上TSV堆叠相连。

B.硅通孔工艺流程

3层堆叠CIS的工艺流程如图10所示。制造过程从晶圆的并行处理开始,每个晶圆都单独连接到各自的基板上。DRAM被翻转接合到逻辑基板的表面。在键合之后,DRAM衬底被减薄至约3μm。然后,形成下部TSV和连接两个基板的金属布线。随后,将像素基板翻转并结合到已经堆叠的DRAM/逻辑基板,然后制作上部TSV以将像素基板连接到堆叠的别的部分。

图10 利用TSV的3层堆叠CIS的工艺流程

C.利用测试模块进行实验验证

研究职员进行了各种测试来剖析三层堆叠CMOS工艺中TSV互连的电学和可靠性特性。研究者们制作了一个300毫米的晶片,带有9000个TSV链,用作测试模块。TSV链从像素层的顶部延伸到DRAM,然后延伸到逻辑衬底。图11显示了9000个TSV链丈量的初始电阻的累积概率。丈量电阻对付任何类型的互连都是至关主要的,由于它们是寄生的,并为流过它们的旗子暗记产生传播延迟。根据结果,研究者得出的结论是:初始电阻很小,不同TSV链之间的电阻值变革很小。此外,利用退火工艺对1260个TSV单元进行了应力迁移测试。在退火过程中,测试模块暴露在175°C下1000小时,图12中的曲线图显示1260个单元的电阻偏移小于2%。电阻的变革是从退火之前和之后打算的。此外,通过在TSV和DRAM基板之间施加1V来丈量TSV和它们之间的泄电流。当采取DRAM时,泄电流是一个关键成分,由于高泄电流会导致DRAM中的低保留存储韶光。从图13中,研究者创造泄露电流非常低,不同单元之间的变革很小。

图11 TSV电阻累积图

图12 TSV应力迁移试验

图13 TSV泄电流

电介质在永劫光暴露于高电场中时会受到破坏并形成导电路径。因此,通过在DRAM和TSV之间永劫光施加180V,在测试模块上进行了韶光干系电介质击穿(TDDB)测试。10000秒后,研究者得出结论,击穿明显减少,这意味着DRAM衬底和TSV之间的绝缘性能足够,如图14展示了在300mm测试模块上进行的实验测试。

图14 TSV TDDB测试

D.三层像素/DRAM/逻辑芯片的研制

在测试模块验证之后,研究者制作了一个3层像素/DRAM/逻辑堆叠芯片,其横截面如图15所示。在图中,像素显示了全体横截面,外围显示了形成像素DRAM和DRAM逻辑衬底连接的堆叠TSV链。上部TSV直径为2.5μm,连接像素和DRAM基板,堆叠芯片中约有15000个TSV。较低的TSV直径约为3.5μm,个中有20000个连接DRAM和逻辑基板。从一个TSV的中央到另一个的TSV节距丈量为6.5μm。

图15 制造的3层堆叠BI-CIS芯片的横截面

只管在像素/逻辑堆栈中添加了第三层DRAM,但研究者得到了与没有DRAM的2层芯片相同的厚度。作为接合工艺的一部分,衬底常日被减薄,减薄后DRAM衬底的终极厚度为3μm。所制造的像素/DRAM/逻辑堆叠BI-CMOS芯片厚度为130μm,像素为1930万,像素大小为1.22μm x 1.22μm,在输出接口处的传输速率为30fps。

3.利用Cu-Cu稠浊键合的堆叠BI CIS(研究者:Y. Kagawa等,2018)本研究中,研究者采取Cu-Cu稠浊键合技能制备了叠层BI-CIS。TSV供应衬底之间的稠浊键合电连接,衬底通过Cu-Cu金属连接电键合,同时通过层间电介质(ILD)物理键合。TSV与Cu-Cu稠浊键合比较险些没有缺点:

TSV须要一种称为深硅蚀刻机的分外制造设备。TSV的制造须要其周围的隔离区(KOZ),这是须要没有任何电路的间隙区域。这限定了电路设计者可用于电路设计的区域。TSV仅供应基板之间的电连接。TSV和Cu-Cu键合的比较如图16所示。值得把稳的是,与TSV比较,Cu-Cu稠浊键合技能须要更少的空间和简化的制造工艺,使其成为空想的选择。它们还为电路设计者供应了更大的设计灵巧性。

图16 TSV(顶部)和Cu-Cu稠浊键合(底部)的比较(Cu-Cu键合的芯片尺寸显著减小)

A.Cu-Cu稠浊键合的工艺流程

Cu-Cu键合工艺从晶圆的制备开始。图17(a)利用化学气相沉积(CVD)在硅上形成厚介电层。CVD因此气相形式沉积固体材料以实现全体表面均匀厚度的过程。然后,制作作为BEOL一部分的沟槽和通孔。利用物理气相沉积(PVD)方法,在沟槽中形成铜籽晶。在PVD之后,利用电化学沉积(ECD)用铜添补沟槽。去除多余的铜,并通过化学机器抛光(CMP)得到非常低的介电粗糙度。在CMP过程中,估量铜会凹陷到一定程度。如图17(b)所示,等离子体活化的晶圆面对面地结合在一起,并且电介质瞬间结合。CMP后,在150°C至300°C的温度下进行退火,因此金属会膨胀以添补它们之间的间隙。上述步骤证明,由于衬底之间的电介质和金属结合,Cu-Cu稠浊键合供应了物理和电连接。

图17 Cu-Cu稠浊键合工艺流程

CMP在得到介电粗糙度和金属凹陷方面起着至关主要的浸染。在标准的Cu-Cu键合工艺中,铜焊盘是凹陷的。本研究采取了可控CMP工艺,故意使铜焊盘突出,并掌握其键合精度。

B.利用测试模块进行实验验证

与上一节的研究类似,Cu-Cu键合的电气和可靠性测试是在300mm的测试晶圆上进行的。300mm晶片具有300万个以4μm间距制造的Cu-Cu连接。除了丈量铜互连的电阻和打仗间距外,还对晶圆进行TDDB测试以丈量芯片寿命。图18和图19分别显示了测试模块的电阻和触点间距丈量值。在将测试晶圆暴露于175°C 1000小时之前和之后丈量的电阻表明,在高温退火工艺之后,电阻值没有显著变革。对付测试晶圆中的300万个Cu-Cu连接,实现了4μm的打仗间距。图19表明,与之前的研究比较,本研究已被证明具有最小的打仗间距。

图18 Cu-Cu互连电阻的丈量值

图19 触点数量与间距的基准

C.Cu-Cu稠浊键合的堆叠BI-CIS的制备

研究者随后利用Cu-Cu稠浊键合技能制造了堆叠的BI-CIS。在标准的Cu-Cu键合工艺中,铜焊盘在CMP工艺中凹陷,金属在退火过程中膨胀和连接,但是在界面处存在结合空隙的问题。因此,在本研究中,引入了可控CMP工艺,以确保基板铜焊盘之间的风雅电连接。在这个专门的过程中,铜焊盘被故意突出,因此,所形成的基板到基板的金属连接是坚固的,没有任何结合空隙。图20描述了堆叠的BI-CMOS的横截面,从中可以明显看出,衬底在结合界面处无空隙地结合。

图20 利用Cu-Cu稠浊键合的堆叠BI-CIS的横截面

在基于Cu-Cu稠浊键合的堆叠式BI-CMOS芯片中,实现了4μm的低打仗间距,这在制造设计灵巧性增强的小型图像传感器芯片方面发挥了主要浸染。制作的芯片分辨率为2250万像素,像素大小为1μm x 1μm。

4.堆叠双层BI-CIS(研究者K.Zaitsu等,2022)几十年来,各行业一贯致力于实现图像传感器的最佳性能,同时致力于减小芯片尺寸。在诸如前文提到的研究中,光电二极管(PD)和像素晶体管共享同一层。因此,可用于增强其任一性能的设计区域受到限定。研究者已经做出了一些努力来增加CMOS图像传感器的密度以得到更好的性能。最近的研究中,一些研究者提出一些方法使像素小型化,进行深度PD并增加其添补因子。只管如此,由于离子注入过程接管了大部分光子,光电二极管的容量并没有提高。另一种提高PD体积的方法须要长布线来连接传感节点,这导致转换增益降落。

A.双层光电二极管/像素晶体管的构造

一项研究事情先容了一种采取三维顺序制造工艺构建的双层堆叠背照式CMOS图像传感器。光电二极管/像素晶体管的两层配置如图21所示,个中光电二极管和像素晶体管独立设计在两个不同的层中,从而为其优化性能创造了机会。

图21 双层堆叠CIS架构

利用图22所示的横截面可以更好地阐明双层堆叠CIS架构。顶层具有光电二极管和传输栅极,第二层具有放大器、选择栅极晶体管、复位栅极晶体管以及连接第一层和第二层的深打仗。光电二极管通过一种称为全沟槽隔离(FTI)的工艺相互隔离。

图22 双层堆叠CIS的横截面

B.设计优化

在顺序制造过程中,很少有优化事情改进了CMOS图像传感器的性能参数,如转换增益(CG)、量子效率(QE)和全阱容量(FWC)。

(1)转换增益:像素转换增益(CG)是AMP(放大器晶体管)为从光电二极管到浮动扩散(FD)节点的电子电荷输出的电压差,图23显示了转换增益的图示。浮动扩散是RST和AMP(放大器晶体管)栅极处的感测节点电容。作为FTI工艺的一部分,须要大量的深打仗来将每个光电二极管连接到其像素晶体管,这增加了FD电容。电容的增加会降落转换增益。因此,为了只管即便减少FD,将深打仗组连接在一起,形成称为亚局部连接的结,如图22所示。亚局部连接减少了浮动扩散,这反过来又增强了转换增益。

图23 转换增益和量子效率

(2)全阱容量:根据研究一篇文章,全阱容量(FWC)定义为在饱和之前可以存储在像素中的电荷量。图24显示了不同像素尺寸的全阱容量,这意味着用更多的光电二极管面积可以得到更高的FWC。在CIS中,利用双光电二极管(PD)是一种常见的过程。传统上,利用硼杂质来隔离双PD,这霸占了光电二极管的体积,从而降落了FWC。在双层构造中,利用减少硼注入的部分FTI来隔离PD。

图24 全阱容量

(3)量子效率:如先前研究所述,量子效率(QE)是衡量成像器件

(4)将入射光子转换为电子的有效性。这如图23所示,常日以百分比表示。换句话说,QE表示光电二极管转换为电子的光子数量。在传统的FTI工艺中,沟槽常日用多晶硅添补,但它接管了部分光并减少了QE。因此,作者采取了氧化硅作为嵌入材料。氧化硅阻挡光在沟槽中被接管,结果,提高了量子效率。

总之,在双层架构中利用添补氧化硅的部分FTI工艺对QE和FWC都是有益的。

C.三维序列集成工艺流程

3D顺序集成工艺是通过一层一层地构建晶圆来实现的。后续集成的寻衅是在不因工艺过程中施加的高温而毁坏底部衬底的情形下制造顶层。传统的并行处理芯片制造包括前端线(FEOL)和后端线(BEOL)制造步骤。FEOL是制造过程的第一部分,个中构建了晶体管、电阻器和电容器等单个组件,并在末了一步BEOL中完成了各层之间的互连。在顺序工艺中,来自光电二极管和像素晶体管层的深打仗通过金属互连连接,金属互连发生在顶层和底层之间。

三维连续集成如图25所示。与并行处理的晶圆不同,在顺序处理中,器件不须要按照预先的样式结合在一起。相反,它是在底层器件之上处理顶层器件。如图25所示,第一步是形成顶层器件,这是通过在图案化晶圆上形成有源层来完成的。这是顶层FEOL,之后蚀刻两层之间的互连并用金属添补以建立层之间的打仗。

图25 三维序列集成工艺流程

在研究中,光电二极管和传输门是底层器件,像素晶体管是顶层器件。为了连接光电二极管和像素晶体管,来自这两个层的深打仗通过金属互连连接。在退火过程中,光电二极管和传输门在顶层形成过程中受到影响的可能性很大。因此,研究者选择了一种得当的介电膜,在顶层制造过程中供应热稳定性。

D.双层CIS的制备及其优化结果

研究者采取顺序集成工艺制作了两层光电二极管/像素CIS,并丈量了图像传感器的性能参数。双层CIS的横截面如图26所示,显示了传输门、像素晶体管、光电二极管和深打仗的位置。所制造的器件具有尺寸为1μm x 1μm的光电二极管。由于部分FTI增加了PD体积,与之前的研究比较,作者实现了12000 e-的高FWC,这在图27中可以看到。

图26 双层构造的横截面

图27 与以前的研究比较优化了FWC

如前所述,QE通过结合部分FTI和利用氧化硅作为沟槽的添补材料而有所改进。QE在530nm波长下增加了19%,如图28所示。与氧化硅比较,多晶硅接管更多的光,这一点通过图29中FTI的横截面仿照得到了证明,这不利于QE。

图28 QE优化-多晶硅FTI与氧化硅FTI

图29 多晶硅FTI(左)和二氧化硅FTI(右)的光接管仿照截面

如图30所示,与没有深打仗的亚局部连接的情形比较,转换增益增加了28%,随机噪声减少了14%。亚局部连接减少了深打仗的数量,并因此减少了浮动扩散电容。

图30 转换增益和随机噪声

5.总 结2022年CMOS图像传感器的市场份额为192.8亿美元,估量到2030年将达到387.8亿美元。这紧张是由于智好手机、数码相机和各种新运用程序的需求不断增加,并且COMS图像传感器能够知足这些需求。各种器件的设计哀求从更好的图像分辨率、减少的图像失落真到提高的增益,同时得到较小的芯片尺寸。本文按韶光顺序回顾了干系研究论文,很明显,制造工艺在图像传感器架构及其性能的转变中发挥了主要浸染。

背照式和堆叠层是标志着CMOS图像传感器开始在智好手机中利用的紧张观点。堆叠层有助于减小芯片尺寸,而背照式提高了传感器性能。基于TSV的添加DRAM层的制造工艺在减少滚动快门失落真和提高图像质量方面发挥了主要浸染。像素侧的读取速率提高到120帧/秒,同时保持相同的读取速率,输出为30帧/秒,确保消费者看不到延迟。后来,采取了Cu-Cu稠浊键合技能,这被证明是一种有效而方便的衬底键合方法,同时成功地供应了设计灵巧性和减小了芯片尺寸。这使得在智好手机中集成多个摄像头成为可能。

末了,我们探究了双层架构,个中像素和光电二极管利用3D顺序集成过程放置在两个不同的层中。除了采取该工艺外,还采取了其他制造技能,如亚局部连接和氧化硅的部分FTI,通过这些技能得到了12000 e-的高FWC,与以前的技能比较,双层架构转换增益提高到28%,量子效率提高了19%。此外,当在图像中捕捉到亮区域和暗区域的不同阴影时,双层架构增加了光电二极管的动态范围,从而提高了图像质量。

估量CMOS图像传感器将连续涌如今智好手机上,并有可能在迢遥的未来取代数码相机。