仿照开关(Analogswitches)是利用仿照器件(JFET或MOS)的特性实现掌握旗子暗记通路的开关,紧张用来完成旗子暗记链路连接或断开的切换功能。由于它具有功耗低、速率快、无机器触点、体积小和利用寿命长等特点,因而,在自动掌握系统和打算机中得到了广泛运用。

仿照开关是一种三稳态电路,它可以根据选通掌握的电平,决定输入与输出的连接状态。当选通掌握处在使能状态时,输出端与输入端是导通状态的;当选通掌握处在非使能状态时,输出与输入是阻断状态时,此时,无论输入旗子暗记如何变革,仿照开关输出均呈高阻状态。

最基本的仿照开关构造如下图所示:

个中,Q1为N沟通JFET(JunctionField-Effect Transistor,结型场效应晶体管),当VGS=0时,源极与漏极之间是导通的,如下图所示:

此时的电路等效如下图所示:

个中,电阻RDS(ON)表示N沟通JFET导通时的漏-源导通电阻rDS(on)(Static Drain Source On Resistance),也是仿照开关的通态电阻RON(”ON” Resistance),此时负载RL两端的电压如下式:

对付多通道的仿照开关芯片,每个通道都有一个通态电阻RON,这些通态电阻之间的差值称为ΔRON(Δ”ON” Resistance Between any two switches)。

仿照开关有一个最大开关电流,即饱和漏极电流IDSS(Zero Gate voltage Drain Current),但有些数据手册中没有这个参数,一样平常在几百毫安以内。

当栅-源电压VGS<VGS(OFF)(栅-源夹断电压,一样平常在-1V~-10V)时,源极与漏极之间是断开的,如下图所示:

此时电路等效如下:

个中,电阻RDS(OFF)表示仿照开关断开时呈现的阻值,应足以达到抑制相邻两个旗子暗记链路相互滋扰,此时负载RL两端的电压如下式:

我们常日将仿照开关表示如下图所示:

个中,O/C表示仿照开关掌握引脚(Open/Close)

用P沟通JFET也可以组成仿照开关,但目前最常用的还是用MOSFET构成的开关,由于MOS技能是大规模数字集成电路的根本,这样可以在同一工艺下将仿照与数字功能实现在同一块芯片上,如下所示:

但是,无论是JFET或MOS构成的仿照开关,它们导通时漏-源通态电阻RDS(ON)都与栅-源电压VGS有关,而在输入旗子暗记Ui的变革过程中,VGS也是一贯随之变革的,如下图所示:

在旗子暗记的传输过程中,真正施加在MOS管栅-源两极的电压VGS=-(15V-UO),而UO是与Ui干系的,如果输入旗子暗记Ui足够大的话,乃至会在旗子暗记传输过程中将MOS管关断,这显然不是我们想要的结果,由于我们的目标是得到一个恒定的(或比较恒定的)导通电阻RON。我们当然也希望导通电阻越小越好,但是在很多运用中,仿照开关的恒定通态电阻(导电率)是最主要的,也便是通态阻抗平坦度RDS(flat),由于它关乎输出电压的精度。

比如,用高精度ADC(模数转换器)进行多路电压旗子暗记采集时,仿照开关的导通电阻RON不必逼迫哀求有多小,但只要它们的导通电阻RON是恒定的,可以在算法年夜将其带来的偏差打消。

用一对互补MOSFET(即CMOS)即可肃清这些缺陷,它的构造如下图所示:

当O/C掌握引脚为高电平时,Q1(PMOS)因栅-源电压VGS<VGS(ON)而导通(PMOS的导通阈值为负电压),同样,Q2(NMOS)因栅-源电压VGS>VGS(ON)而导通(NMOS的导通阈值为正电压),如下图所示:

此时仿照开关的导通电阻为两个MOS管导通电阻RDS(ON)的并联,它们的特性曲线如下图所示:

NMOS管在旗子暗记比较低时的导通电阻较小,而PMOS管则在输入旗子暗记较高时的导通电阻较小,两个电阻并联后,则在全体旗子暗记的有效范围内都比较低。

当O/C掌握引脚为低电平时,两个MOS管均为阻断状态,如下图所示:

有些数据手册也会给出这个导通电阻的信息,如下图所示:(来自intersil的CD4051数据手册)

这种基本的构造也叫做传输栅,有些规格书中以下面的符号表示:

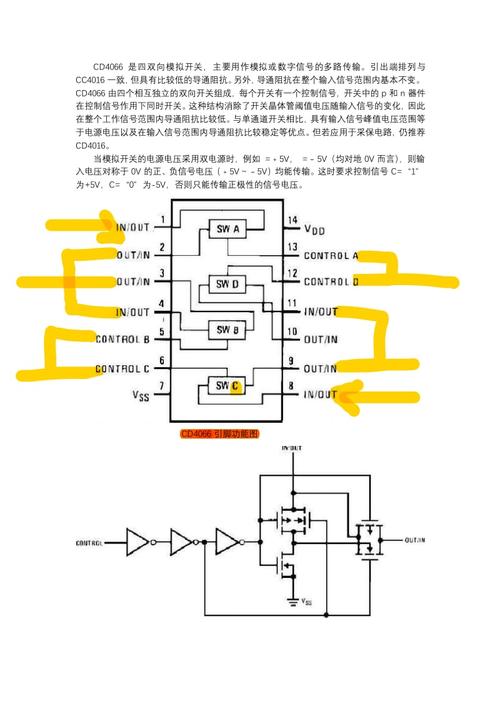

比如,CD4066的事理框图如下所示:(下图来自UTC的CD4066数据手册)

既然仿照开关由MOS管构成,自然也有相应频率相应的最大值,这个值常日可以达到数十兆,它包含两种情形:即开关分别在导通状态下与阻断状态下频率相应。开关在导通状态下的频率相应(FrequencyResponse-Switch “ON”)比较好理解,便是在仿照开关导通状态下,旗子暗记能够通过的最大频率,那么阻断状态下的频率相应又是个神马东西?如下图所示:(以下均来自UTC的仿照开关CD4066数据手册)

个中,Feedthrough –Switch “OFF”表示在仿照开关阻断状态下的馈通频率,我们看看Fig.4的测试电路图,如下所示:

上图已经说了,当VCON=VSS(即仿照开关阻断时)时,电路用来测试馈通(Feedthrough)状态下的频率相应。理论上,在仿照开关阻断状态下,无论有没有输入旗子暗记VIS,其相应的输出VOS是不会有输出的,但是MOS管本身是有寄生电容的(如上表中的CIO,也称为CDS,即漏极-源极电容),在关断状态下如果输入旗子暗记频率超过一定值,那旗子暗记就阻断不明晰,它会通过电容CIO以高频耦合的办法通过开关,使得开关呈现导通状态。如下图所示:

还有一个参数是掌握引脚的最大开关频率(Maximum Control Input),一样平常我们说仿照开关的速率便是指这个参数,而不是上面提到的频率相应的最大值。它的测试电路如下所示:

仿照开关芯片有多个通道时,通道与通道间也会有旗子暗记的串扰,这与PCB板走线串扰是同样的道理,如下图所示:

它是指没有输入旗子暗记的选通通道(下侧)吸收到来自相邻通道(上侧)旗子暗记引起的滋扰,即VOS(2),把稳表格中的测试条件:下侧的VCON(2)=VSS不是0,而是5V,也便是选通状态。

同样,当掌握引脚VCON在导通与阻断状态切换时,也会在旗子暗记通道上产生相应的串扰,如下图所示: