0 弁言

高速数据采集广泛运用于雷达、电子对抗、航空航天、导弹测控、仪器仪表、图像处理、高性能掌握器等领域,是当代电子设备中的技能关键。随着打算机、通信和微电子技能的高速发展,人们不断地对数据采集的速率和精度提出更高的哀求,然而受芯片制造工艺的限定,超高速ADC采样芯片的特性难以知足高性能设备的需求[1]。采取多片高速ADC芯片并行交替采样,实现超高速和高精度采样,是办理此类问题最为有效的方法。本文利用N路高速ADC芯片对一起仿照旗子暗记并行交替采样,然后对各路采样得到的数据依次拼接,使得全体系统采样频率为单块A/D芯片的N倍,在保持高精度的同时成倍地提高系统的采样率,达到超高速的采样目的。

1 高速并行数据采集系统构造

本设计首先将一起10 MHz、10 Vpp的高频仿照旗子暗记分别接入两路12位A/D芯片的输入接口,然后通过FPGA对两路A/D芯片分别以50 MHz的速率并行交替采样10 ms,将转换的采样数据存储到SDRAM中,存储的数据可以通过串行接口送到上位机处理,全体系统硬件构造如图1所示。

10 MHz正弦波旗子暗记通过旗子暗记发生器产生,该旗子暗记的输出频率及幅值大小可以根据实际须要进行调度。模数转换芯片采取ADI的AD9226芯片,AD9226是一款单路、12位、65 MS/s模数转换器,采取单电源供电,内置一个片内高性能采样保持放大器和基准电压源。它采取多级差分流水线架构,数据速率达65 MS/s,在全体事情温度范围内担保无失落码[2]。FPGA芯片采取Altera公司所生产的Cyclone IV系列芯片EP4E6F17C8,其具有低本钱、低功耗的FPGA系统构架;内部具有大量嵌入式存储器和逻辑单元,可以通过NIOS软件构成软核处理器。本设计外部存储器选择SDRAM,其型号为HY57V2562GTR,容量为256 Mit(16 M×16 bit),具有16 bit总线。本设计通过NIOS可以天生EP4E6F17C8与外部存储器的接口,包括有SDR、DDR、DDR2等。

一起仿照旗子暗记同时输入至两路A/D转换芯片输入端,为了使旗子暗记相位相同,可以通过PCB的等长走线来实现。由于本设计A/D转换哀求输入电压在1~3 V之间,以是须要将旗子暗记发生器的±5 V旗子暗记进行调理。AD8065放大器为电压反馈型放大器,供应FET输入,事情噪声极低(7.0 nV/Hz和0.6 fA/Hz),输入阻抗较高,带宽为145 MHz,适宜各种运用[3]。VREF为AD9226输出+2.5 V参考电压,通过NE5532二级运放构成增益为-1的电压跟随,终极输出-2.5 V的参考电压,参考电压通过AD8065进行差分运算。增益调理电路如图2所示,通过运算放大器AD8065将互换旗子暗记调理至1~3 V送至模数转换芯片的输入端。

模数转换芯片选择AD9226,本设计采取SSOP封装形式,AD9226的D0~D11引脚为模数转换的数字输出量,当时钟旗子暗记送至AD9226的1脚时,将触发一次模数转换,在模数转换中D0~D10为数据位,而D11为符号位,OTR为模数转换的溢出标志。由于A/D转换的电路比较大略,这里就不列举,详细内容请参阅其数据手册。

全体系统采取FPGA掌握,与相对顺序操作的单片机或者ARM掌握比较,其具有无法比拟的上风。FPGA采取的是并行处理的可编程逻辑器件,通过FPGA实现数据的高速采样、读取、存储及处理等操作。EP4CE6F17C8的外部时钟源为50 MHz,可以通过PLL进行倍频。由于FPGA内部没有程序存储单元,以是须要外部扩展,本设计采取M25P16(或EPCS16),其本色是一个容量为16 Mbit的串行Flash芯片,这对付存储FPGA中的程序绰绰有余,同时还可以存储软核NIOS II的运用程序。

在本设计中,FPGA与A/D转换模块接口、存储器模块接口以及PLL时钟旗子暗记都可以通过开拓软件Quartus在SoPC(System on a Programmable Chip)中建立。SoPC用可编程逻辑技能把全体系统放到一块硅片上,用于嵌入式系统的研究和电子信息处理,是一种分外的嵌入式系统。它是片上系统(SoC),即由单个芯片完玉成部系统的紧张逻辑功能,但它又不是大略的SoC,它具有灵巧的设计办法,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。通过Quartus软件在SoPC上建立的软核如图3所示,PLL为锁相环,输出C0~C3四路时钟旗子暗记,C0作为软核kernel的时钟源。由于SDRAM哀求时钟频率为100 MHz,而FPGA外部时钟旗子暗记为50 MHz,以是须要对C1进行2倍频。C2和C3为两路A/D采样的时钟旗子暗记,由于相位相差180度,可以通过时钟相位偏移设置,本文在C3的输出旗子暗记线上加入一个非门,来实现两路时钟旗子暗记的180度相位偏转,用逻辑剖析仪采集的两路时钟旗子暗记相位波形如图4所示。AD1_DB[11..0]和AD2_DB[11..0]将外部两路A/D采样转换后的数据输入FPGA。

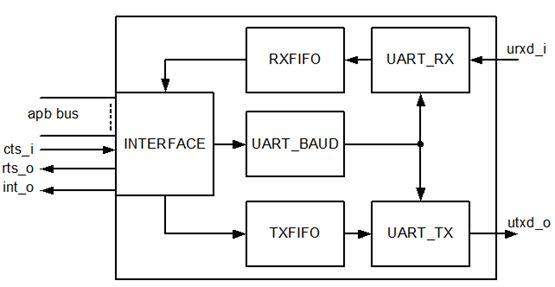

两路A/D采样精度为12 bit,同时以50 MHz的速率交替采样,则数据量将达到1.2 Gb/s,这个数据量是相称大的,目前打算机普通数据传输速率远达不到此哀求。以是本设计以微秒为单位,只采集有限个点的数据,将采集的数据暂存入SDRAM中。两路A/D转换有严格的时序关系,由图3可知AD2的采样时钟旗子暗记比AD1的延迟180度,为了保持旗子暗记严格时序,系统在读取AD1当前采样数据的同时,读取前一次AD2的采样数据,而数据存储格式为AD1_DB[11..0]+AD2_DB[11..0]共计24位,低位存AD1的数据,高位存AD2的数据(由于各通道采样韶光间隔为20 ns,而相位相差180度,以是在数据采集过程中没有包含韶光量)。等到采样结束后,将采集的数据转换为字符串,通过串行接口送至上位机进行剖析处理。全体软件通过NIOS调用Quartus软核,个中A/D采样及SDRAM的读写比较大略,这里就不做详细先容,而串行接口的读写可以参考相应的例程资料。

2 实验数据剖析及结论

为了验证实验的有效性,通过旗子暗记发生器在系统的输入端输入一个10 Vpp、10 MHz的正弦旗子暗记,系统对该旗子暗记连续采样1 000组数据存入SDRAM,然后将数据通过串口发送至上位机。得到的两路数据终极以Excel数据格式存储。随机提取连续的100组采样数据,通过MATLAB对数据进行处理,将数据转换成连续的点。各通道采样点的连线与整合后的采样点连线如图5所示,MATLAB数据处理程序如下:

x1=caiyang1(:,1);

y1=caiyang1(:,2)/20485;

subplot(3,1,1);

title(′一通道采样点连线′);

line(x1,y1,′Marker′,′+′);

grid on;

x2=caiyang2(:,1);

y2=caiyang2(:,2)/20485;

subplot(3,1,2);

title(′二通道采样点连线′);

line(x2,y2,′Marker′,′′)

grid on;

x3=honghe(:,1);

y3=honghe(:,2)/20485;

subplot(3,1,3)

title(′整合后采样点连线′);

line(x3,y3,′Marker′,′.′)

grid on;

通过图5可知,整合后的交替高速数据采集系统的采样精度有了大幅提高。以是,采取韶光交替技能的并行数据采集系统,能在担保采样精度的情形下最大限度地提高采样速率。在超高速数据采集系统的构建上提出了一种新的办理方法,使得超高速数据采集成为可能,对超高速仪器仪表的研究发展具有重大的借鉴意义。

参考文献

[1] 李玉生.超高速并行采样仿照/数字转换的研究[D].合肥:中国科学技能大学,2007.

[2] ANALOG DEVICE. AD9226 DATA SHEET(Revision .0)[Z]. 2000.

[3] ANALOG DEVICE. AD8065/AD8066数据手册(Revision.J)[Z]. 2010.