AM3358开拓板

阅读提要

本PCB设计指南由德力威尔王术平根据《AM335X英文数据手册2013版》之DDR3章节翻译、编撰而成,包含AM3358处理器简介、DDR3与MPU电路连接、PCB堆叠设计、DDR3与MPU布局、DDR3布线区、旁路电容参数与位置、DDR3旗子暗记分组、DDR3终端电阻、DDR3参考电压布线、DDR3数据线走线拓扑与布线规则等实用内容,供广大PCB设计者参考学习。

图1 AM3358功能框图

一、AM3358与DDR3硬件平台简介1.1. AM3358微处理器

型号:AM3358BZCZA100

主频:1GHz

焊球数量:324pin

焊球直径:0.5mm

紧张特色(见图1):

●ARM Cortex-A8架构,主频1Ghz,32位RISC微处理

●支持LPDDR、DDR2、DDR3、DDR3L接口

●支持NAND Flash、NOR Flash、SRAM

●3D 图形引擎

●LCD和触摸屏掌握器

●可编程RTC和工业通信子系统

●两路USB 2.0,支持OTG

●10/100/1000M以太网

●2路CAN掌握器、6路UART、2路MCASP音频、2路SPI、3路I2C

●12Bit ADC

●3路32位增强型捕获模块

●3路增强型高精度PWM

1.2 DDR3动态存储器

型号:IS43TR16256A-15HBLI

容量:4Gbit(256M x 16)

速率: DDR3-1333Mbps

电压:1.5V

温度:-40℃~95℃

焊球数量:96 pin

焊球直径:0.5mm

时钟:DDR_CK and DDR_CKn事情的标准速率是303 MHz

数据位宽度:16bit

芯片个数:单片

二、AM3358和DDR3电路连接办法

本产品采取单个DDR3和MPU连接,数据宽度为16Bit,外部没有VTT闭幕器。连接示意如图2所示:

图2 MPU和DDR3连接关系

三、PCB堆叠设计3.1 PCB叠层

DDR3布线部分至少须要4层板,可以再增加层数,用来走其他的旗子暗记或者增强旗子暗记完全性和提高电磁兼容抗滋扰能力,优先考虑将旗子暗记布在第一层,第一层布不完时可以布在第四层,但第四层的走线不能超过第三层电源分割面。PCB叠层如图3所示:

图3 PCB最少叠层方案

3.2 PCB叠层规则

图4 PCB堆叠规范

如图4所示:

PCB走线层和平面层一共不低于4层;旗子暗记层不低于2层;在DDR3布线区域的参考电源平面和参考地平面要完全,地平面优于电源平面,当走线层切换时,确保有旁路电容供应高频返回路径;以增强SI完全性、抑止EMI。DDR3走线线宽范例值在4mil;过孔尺寸范例值在10mil/18mil或10mil/20milAM3358ZCZ BGA 焊盘尺寸直径为0.5mm单端特色阻抗在50~75欧姆,偏差掌握在+-5欧姆。四、AM3358和DDR3布局方法图5 DDR3布局规范

如图5所示:

DDR3布线区域只能走DDR3干系旗子暗记线,禁止其他走线;DDR3芯片中央水平方向离MPU芯片中央最远的间隔≤X1+X2(≤1600mil);DDR3芯片中央垂直方向离MPU芯片中央最远的间隔≤Y(≤1500mil);其他走线离DDR3走线区边到边保持4倍线宽以上;DDR3离MPU越近,旗子暗记传输时延裕量就越大,传输就越稳定;其他旗子暗记线走线要与DDR走线区用地平面隔开。五、DDR3布线区域DDR3布线区域同层内不许可其他非DDR3旗子暗记走线,DDR3布线区域的参考平面一定要完全的DDR电源平面或地平面,非DDR3旗子暗记可以布在DDR3布线区域下面有完全参考平面隔离的层内,如图6所示。

图6 DDR3布线区

六、大容量低频旁路电容的利用

MPU、DDR3须要大体积、大容量的旁路电容。大体积旁路电容只管即便靠近MPU和DDR3的电源引脚。但优先考虑小体积高频旁路电容和DDR旗子暗记布线空间,然后再考虑大体低频积旁路电容。

图7 大容量旁路电容运用规范

如图7所示:

AM3358 VDDS_DDR电源引脚大容量旁路电容的个数≥2,大电容总容量≥20uF;担保每一颗DDR3芯片电源引脚大容量电容的个数≥2,大电容总容量≥20uF;大电容只管即便先知足DDR3芯片,靠近芯片电源引脚布局。七、小容量高频旁路电容的利用DDR3的正常运行是离不开高频旁路电容的,并且要只管即便减小连接在DDR电源和地之间的高频旁路电容的寄生电感。常日来说,至少做到以下几点是比较好的:

1、安装的高频旁路电容尽可能的多一点;

2、只管即便减少旁路电容到须要旁路的CPU或DDR芯片上的电源引脚之间的间隔;

3、利用物理尺寸只管即便小中容量只管即便高的旁路电容;

4、旁路电容打过孔的孔径只管即便大,旁路电容焊盘到它的过孔之间的连线只管即便要宽;

5、只管即便不要多个旁路电容的焊盘共用一个焊盘。

下表是关于高速旁路电容利用把稳事变(如图8):

图8 小容量旁路电容运用规范

如图8所示:

高速旁路电容的封装尺寸为0201或0402;高速旁路电容焊盘中央离被旁路的AM3358的电源引脚和地引脚间隔越近越好,建议≤400mil;AM3358的VDDS_DDR 须要高速旁路电容的个数≥20,总容量≥1uF;连接过孔离AM3358的VDDS_DDR和地引脚越近越好,范例值≤35mil,最长不超过70mil;高速旁路电容焊盘中央离被旁路的DDR3的电源引脚和地引脚间隔越近越好,建议≤150mil;DDR3高速旁路电容的个数≥12,总容量≥0.85uF;高速旁路电容到被旁路的电源和地引脚连线的过孔个数≤2;过孔的离电容焊盘的走线长度范例值≤35mil,最长≤100mil;高速旁路电容到DDR3的电源和地引脚过孔个数≤1,过孔离引脚的走线长度范例值≤35mil,最长≤60mil;两个高速旁路电容分别在顶层和底层镜像布局,则可以共用一个过孔;10.旁路电容和电源引脚和地引脚可以共用一个过孔;

11.DDR3一对电源可以共用一个过孔,一对地引脚可以共用一个过孔。

八、DDR3旗子暗记分组8.1 DDR3的时钟网络分组

图9 时钟组定义

CK主时钟组(差分对):DDR_CK& DDR_CKn;

DQS0数据同步时钟组(差分对):DDR_DQS0& DDR_DQSn0;

DQS1数据同步时钟组(差分对):DDR_DQS1& DDR_DQSn1;

8.2 DDR3地址/数据旗子暗记网络分组

图10 旗子暗记组定义

CA地址掌握组(单端线):DDR_BA[2:0]、DDR_A[15:0]、DDR_CSn0、DDR_CASn、DDR_RACSn、

DDR_WEn、DDR_CKE、DDR_ODT,以CK时钟组对齐;

DQ0字节组(单端线):DDR_D[7:0]、DDR_DQM0,以DQS0时钟组对齐;

DQ1字节组(单端线):DDR_D[15:8]、DDR_DQM1,以DQS1时钟组对齐。

九、DDR3旗子暗记终端电阻运用

本例中DDR3芯片内含有针对DQS[x]和DQ [x]的ODT(片内闭幕器),而CK和ADDR_CTRL既没有内部的ODT,也没有外接VTT闭幕器,但这并不影响旗子暗记完全性,可以这样运用。

十、DDR3的 参考电压DDR_VREF布线

DDR_VREF走线宽度常日为20mil(0.508mm),如果布线空间有限可适当减小宽度。在MPU和DDR的每个DDR_VREF电源引脚附近,就近要放置一个0.1uF的高频旁路电容。

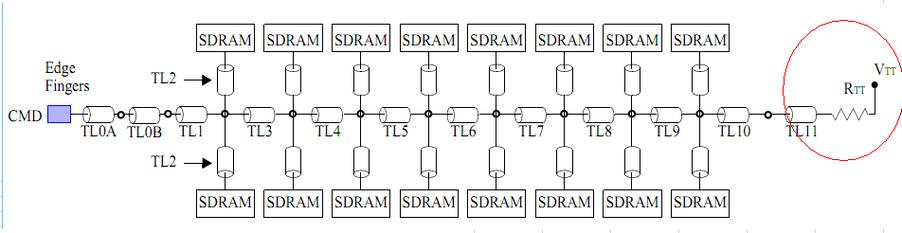

十一、DDR3的 CK和ADDR_CTL拓扑和布线规则11.1 CK和ADDR_CTL拓扑

图11 CK组合CA组布线拓扑

所选DDR3型号的CK和CA旗子暗记如需并联端接电阻,就按上图所示拓扑布线;所选DDR3型号的CK和CA旗子暗记若无需并联端接电阻,忽略AT走线,忽略并联端接的电阻、电容器。本项目所选DDR3型号为后者。

11.2 CK和ADDR_CTL走线

图12 CK组合CA组布线方法

所选DDR3型号的CK和CA旗子暗记如需并联端接电阻,就按上图所示布线;所选DDR3型号的CK和CA旗子暗记若无需并联端接电阻,忽略AT走线,忽略并联端接的电阻、电容器。本项目所选DDR3型号为后者。

十二、DDR3的DATA线走线拓扑与走线规则12.1 DATA线拓扑

图13 DATA线拓扑

数据对齐时钟DQS[x]是点到点的差分旗子暗记线,所有数据线DQ[x]是点到点的单端旗子暗记线。

12.2 DATA线布线方法

图14 DATA线布线方法

数据对齐时钟DQS[x]是点到点的差分布线,所有数据线DQ[x]是点到点的单端布线。

十三、DDR3布线长度规则13.1 CK和ADDR_CTL布线长度规则

CK组内差分线要匹配等长;

ADDR_CTL(CA)组内的各个旗子暗记线要以CK组为对齐基准,匹配等长;

CK和ADDR_CTL(CA)走线的最大长度可以采取下图的曼哈顿间隔来确定:

图15 曼哈顿间隔打算最长走线

一旦MPU和DDR3的位置固定下来后,采取上图中曼哈顿间隔确定的布线长度便是最长布线长度了;CK和ADDR_CTL(CA)以此线作为基准长度,只管即便减少长度偏移;

多个DDR3时,接入DDR3的短的树桩线和外接VTT终真个短的树桩线,不包含在长度打算内。

最长布线长度打算公式:CALM=CACLMY+CACLMX+300mils;此处额外的300mils浸染是给布线空间留有充足的余量,这里CACLMY=A1,CACLMX=A2+A3,以是CALM=A1+A2+A3+300mil=2500mil+660mil+300mil=3460mil。

CK和ADDR_CTL(CA)布线长度详细规则如图16所示:

1、(A1+A2)长度≤2500mil,许可偏差长度≤25mil;

2、A3长度≤660mil,许可偏差长度≤25mil;

3、单端线AS长度≤100mil,许可偏差长度≤25mil;

4、差分线AS+和AS-长度≤70mil,许可偏差长度≤5mil;

5、单端线端接电阻走线AT长度≤500mil,许可偏差长度≤100mil;

6、差分线端接电阻走线AT长度≤500mil,许可偏差长度≤5mil;

7、CK组合CA组范例的长度为CALM+-50mil;

8、CK线和其他DDR3走线间距≥4W原则(线中央到线中央);

9、CA线和其他DDR3走线间距≥4W原则(线中央到线中央);

10、CK差分对内部间距要知足阻抗匹配的;

11、CK线到其他非DDR3旗子暗记线之间的间隔≥4 W原则(线中央到线中央);

12、Rcp端接电阻为特色阻抗Zo+-1Ω,Rcp端接电阻为特色阻抗Zo+-1Ω,Rtt端接电阻为特色阻抗Zo+-5Ω,单端特色阻抗Zo为50~75欧姆,差分特色阻抗Zo为单端特色阻抗的2倍。

图16 CK组和CA组布线长度规则

图中(n)备注:

(1)CK表示时钟旗子暗记网络组,ADDR_CTRL表示地址、掌握旗子暗记网络组;

(2)只管即便利用最少数量的过孔;

(3)当要在DDR3电源层作为参考平面打过孔换层时,须要添加返回电流旁路电容;

(4)镜像放置;一个放置在顶层、一个放置在底层,呈镜像重合状。

(5)非镜像放置:所有的DDR3在同一层;

(6)只管即便减小走线长度;

(7)只针对ADDR_CTRL网络组,建议减小长度偏移,但不是必须的;

(8)只针对CK网络组;

(9)CACLM是最长的曼哈顿间隔;

(10)当走线长度超过1250mils时,许可适当减小线中央到线中央的间隔;

(11)不同DDR3的旗子暗记线;

(12)CK是差分阻抗欧姆,差分阻抗是单端阻抗的2倍;

(13)外接的VTT闭幕器是绝对不许可放置在源端(CPU驱动端)。

13.2 DQS[x]和DQ[x]布线长度规则

不建议,也不必将所有的数据线匹配等长,但将每1字节的数据匹配等长是必须的。可用曼哈顿间隔确定最长走线长度。

图17 曼哈顿间隔确定DQ组布线最长长度

图18 DQ组布线长度匹配规则

如图18所示:

1、DQS和DQ线有内部ODT功能,不许可外接终端匹配电阻;

2、DQ0数据组标称长度≤DQLM0(数据0组的曼哈顿间隔),许可偏差长度≤25mil;

3、DQ1数据组标称长度≤DQLM1(数据1组的曼哈顿间隔),许可偏差长度≤25mil;

4、DQS0数据对齐时钟和DQ0数据组一样长,许可偏差长度≤25mil;

5、DQS1数据对齐时钟和DQ1数据组一样长,许可偏差长度≤25mil;

6、DQ0组(含DQS0)与DQ1组(含DQS1)不用等长,以各自的字节对齐即可;

7、DQ[x]组内走线间距≥3W原则(线中央到线中央);

8、DQ[x]和其他DDR3走线间距≥4W原则(线中央到线中央);

9、DQS[x]组内间距应知足差分阻抗;

10、DQS[x]和其他DDR3走线间距≥4W原则(线中央到线中央);当走线长度超过1250mils时,间距许可降到最小的4W原则;

11、TI官方文档规定了CK时钟线和ADDR_CTRL线匹配等长,DQS[x]与DQ[x]匹配等长,但是并没有规定CK和DQS[x]匹配等长。但依据德力威尔王术平的设计履历,建议掌握DQS(含DQ)布线长度小于CK布线长度,DQS(含DQ)线只管即便最短。

十四、AM3358之DDR3布线规范总结

1.走线最长≤63.5mm

2.地址/掌握组以时钟组对齐,长度偏差为2.54mm;数据组一定要比时钟组走线长度要短,只管即便最短;

3.时钟组组内长度偏差0.127mm

4.地址组组内长度偏差0.635mm

5.数据组内DQS对之间偏差0.127mm

6.数据组内DQ组内偏差0.635mm

7.数据组内DQS与DQ之间偏差0.635mm

8.数据组DQS0与DQS1两对之间偏差不限,但只管即便短;

9.所有线与CLK对齐(Address>CLK>Data)

10.数据0组以DQS0&DQSN0对齐

11.数据1组以DQS1&DQSN1对齐

12.DQS0与DQS1组与CLK组对齐

13.所有地址组与CLK组对齐

14.CPU电源、地焊盘打孔引线≤1.778mm

15.CPU退耦电容打孔间隔CPU焊盘≤10mm

16.退耦电容一个焊盘上打孔≥2个

17.CPU电源焊盘打孔≥1个

18.DDR3电源、地引脚焊盘打孔引线≤1.54mm

19.DDR3退耦电容打孔与DDR3电源引脚间隔≤3.81mm

20.DDR3退耦电容一个焊盘打孔≥2个

21.DDR3电源、地引脚打孔≥1个

22.DDR3_VREF基准电源线宽度:0.508mm/3W

23.CLK、Address、Data组外间距4W,组内间距3W

24.DDR3的数据引脚靠近CPU一端

25.CPU和DDR3布局的间距:水平25.4mm 垂直38.1mm 之内

26.走线长度=曼哈顿间隔+7.62mm

德力威尔电子工程师培训中央PCB培训实例

更多PCB培训、PCB设计培训、电路板培训以及学习PCB设计的技能资料,请参考德力威尔王术平的其他技能博文或者上岸德力威尔电子工程师培训中央官方网站下载。

作者简介:德力威尔王术平,嵌入式软硬件全能设计工程师,运用电子技能独立研究员,运用电子技能授课讲师,德力威尔电子工程师培训学校创始人。

本文由德力威尔王术平原创,欢迎点赞、收藏及转发;严禁搬运、抄袭及转载;全网维权。