封装曾经是半导系统编制造过程中的事后想法,不被大家重视。当你创造了这一小块神奇的硅片之后,然后把他用某种方法封装起来,同时引出管脚,一颗芯片就出身了。但是随着摩尔定律的延伸,工程师们意识到,他们可以利用对芯片的所有部分,包括封装在内进行优化和创新,来制造出最好的产品。

更令人惊异的是,过去没有一家封装公司被认为像传统的前端制造工艺那样主要。封装供应链常日被认为是"后端",并被视为本钱中央,类似于银行业的前台和后台。但现在,随着前端难以更好的缩小芯片尺寸,一个全新的关注领域已经涌现,这便是对前辈封装的重视。

接下来我们谈论一下封装的发展简史,从大略的DIP封装一贯到前辈的2.5D或3D封装。

封装发展简介

这是我从这个精彩的视频座中创造的封装技能的简要层次构造。如果你有一些韶光,可以看一下。(视频揭橥于2012年,但是当时已经提到了现在最新的3D封装技能,以是并不过时)

封装技能一个简化的演化过程是:DIP>QFP>BGA>POP/SiP>WLP

显然,有很多不同的封装技能,但我们要谈论的是大致能代表每种类型的大略技能,然后逐步将其带到现在。我也非常喜好下图这个高层次的概述(不过它已经由时了,但仍旧精确)。

在封装的最初阶段,裸片常日采取陶瓷或金属罐封(气密),以实现最大的可靠性。这紧张适用于航空航天和军事运用,这些功能须要最高水平的可靠性。然而,对付我们的大多数日常用例来说,这并不是真正可行的,以是我们开始利用塑料封装和双列直插封装(DIP)。

DIP封装(1964-1980年代)

最早的DIP包装元件是由仙童半导体司的Bryant Buck Rogers在1964年时发明,在表面贴装技能问世之前的十年里,它被广泛运用。DIP在实际的裸片周围利用塑料封装外壳(编辑注:实际上陶瓷封装的军品芯片也大批采取了DIP封装),并有两排平行的突出的引脚,称为引线框架,与下面的PCB(印刷电路板)相连。

实际的芯片通过键合线连接到两个引线框架,两个引线框架可以连接到印刷电路板(PCB)。DIP封装以复古的办法具有标志性,设计选择是可以理解的。实际的裸片将完备密封在树脂中,因此它带来了高可靠性和低本钱,并且许多首批标志性的半导体都因此这种办法封装的。请把稳,芯片通过导线连接到外部引线框架,这使其成为一种"引线键合"封装方法。稍后将对此进行详细先容。

下面是英特尔8008--实际上是第一批当代微处理器之一。把稳它的标志性DIP封装。因此,如果你看到那些看起来像小蜘蛛的半导体的时髦照片,这只是一个DIP封装类的半导体。

英特尔的原始微处理器,8008 家族

然后,这些小金插针中的每一个都被焊接到PCB上,在那里它与其他电气元件和系统的别的部分打仗。以下是封装如何焊接到PCB板上。

PCB本身常日是由铜或其他电气元件由非导电材料层压而成。然后,PCB板可以将电旗子暗记从一个地方运送到另一个地方,并让个元件相互连接和通信。

虽然DIP还有其他演绎版,但实际上是时候转向始于20世纪80年代的下一个封装技能范式或表面贴装封装了。

表面贴装封装(1980-1990年代)

下一步的变革不是通过DIP安装产品,而是引入表面贴装技能(SMT)。正如所暗示的那样,封装直接安装在PCB的表面上,并许可在一块基板上利用更多的元件并降落本钱。下图是范例的表面贴装封装。

上面描述的许多封装方案本日仍在利用,但是,您将开始看到越来越多的封装类型,并且这些封装类型将来会变得更加干系。公正地说,许多这些即将到来的技能是在过去几十年中发明的,但由于成本原因,直到后来才被广泛利用。

这个过程曾经是手动的,但现在是高度自动化的。此外,这实际上为PCB创造了相称多的问题,如popcorning。封装爆裂是指在焊接过程中,塑料封装内的水分被加热,由于快速加热和冷却,水分在PCB上造成问题。另一件须要把稳的事情是,随着封装工艺的每一次提升,繁芜性和故障也会随之增加

球栅封装和芯片级封装(1990年代至2000年代)

随着对半导体速率的需求不断提高,对更好封装的需求也在不断增加。虽然涌现了QFN(四方扁平无引线)和其他表面贴装技能,但我想向你先容一种我们在未来必须理解的封装设计的开端,这便是广泛利用的球栅阵列(BGA)封装的开始。

这些焊球或突出被称为焊料突出/球

这便是球栅阵列的外不雅观,可以从下面直接将一块硅片安装到PCB或基板上,而不是像以前的表面贴装技能那样大略地将所有4真个角落贴上胶带。

因此,这只是我上面列出的趋势的另一个延续,占用更少的空间,有更多的连接。现在,我们不再是用电线细细地连接每一侧的封装,而是直接将一个封装连接到另一个。这导致了密度的增加,更好的I/O性能,以及现在增加的繁芜性,即你如何检讨BGA封装是否事情。在这之前,封装紧张是通过视觉检讨和测试。现在我们无法看到封装,以是没有办法进行测试。我们可以X射线进行检讨,以及更繁芜的技能。

当代封装(2000-2010年代)

我们现在走进了当代封装的时期。

上面描述的许多封装方案本日仍在利用,但是,您将开始看到越来越多的封装类型,并且这些封装类型将来会变得更加干系。公正地说,许多这些即将到来的技能是在过去几十年中发明的,但由于成本原因,直到后来才被广泛利用。

倒装芯片

这是你可能会读到或听到的最常见的封装之一。我很高兴能为你定义它,由于到目前为止,我读过的入门书中还没有一个令人满意的阐明。倒装芯片是IBM很早就发明的,常日会被缩写为C4。就倒装芯片而言,它确实不是一种独立的封装形式,而是一种封装风格。它险些便是只要在芯片上有一个焊接凸点就可以了。芯片不是用线粘合互连,而是翻转过来面对另一个芯片,中间有一个连接基板,以是叫 "倒装芯片"。

从维基百科上的阐明内容可以更好的理解什么是倒装芯片:

1. 在晶圆上创建集成电路

2. 芯片表面的焊盘被金属化

3. 每个焊盘上都沉积一个焊点

4. 芯片被切割

5. 芯片被翻转和定位,以便焊球面向电路

6. 然后将焊球重新熔化

7.安装好的芯片用电绝缘胶进行底部添补

引线键合

请把稳倒装芯片与引线键合有何不同。上面先容的DIP封装这便是引线键合,个中芯片利用导线键合到另一种金属上,然后焊接到PCB上。引线键合不是一种特定的技能,而是一套较旧的技能,涵盖了许多不同类型的封装。引线键合是倒装芯片的前身。

前辈封装(2010年代至今)

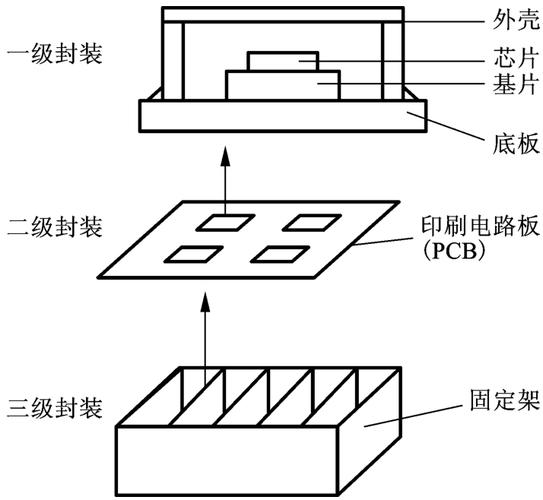

我们一贯在缓慢地进入"前辈封装"半导体时期,我现在想谈谈一些更高等的观点。实际上,有各种层次的"封装"适宜这个思维过程。我们之前讲过的大多数封装,都集中在芯片封装到PCB上,但前辈封装的开始实在是从手机开始的。

手机在很多方面都是前辈封装诸多方面的巨大前奏。这是有道理的!

对付手机须要在尽可能小的空间内集成大量的芯片,比条记本电脑或台式电脑密度大得多。所有东西都必须被动冷却,当然也要尽可能薄。这将封装推向了新的极限。我们谈论的许多观点都是从智好手机封装开始的,现在已经将自己推向了半导体行业的其他部分。

芯片级封装(CSP)

芯片级封装实际上比听起来要宽一些,最初意味着芯片大小的封装。技能定义是封装尺寸不超过芯片本身的1.2倍,并且必须是单芯片且可连接的。实际上,我已经向您先容了CSP的观点,那便是通过倒装芯片。但CSP确实通过智好手机提升到了一个新的水平。

这张照片中的所有东西都是芯片芯片的1.2倍大小,并且专注于节省尽可能多的空间。CSP时期有很多不同的风格,包括倒装芯片、右基板和其他技能,都属于这一类。

晶圆级封装(WLP)

但还有一个更小的级别--这便是 "终极 "芯片规模的封装尺寸,或在晶圆级封装。这险些便是把封装放在实际的硅片本身。封装的便是硅片。它更薄,具有最高水平的I/O,而且显然会非常热,很难制造。前辈的封装革命目前是在CSP的规模上,但未来将集中在晶圆上。

这是一个有趣的演化,封装被实际的硅本身所包含。芯片是封装,反之亦然。与仅仅将一些球焊接到芯片上比较,这真的很昂贵,那么我们为什么要这样做呢?为什么现在对前辈封装如此痴迷?

前辈封装:未来

这是我长期以来一贯在描述的趋势的一个顶峰。异构打算不仅是专业化要做的事,而且是我们如何将所有这些专业化的碎片放在一起的事。前辈的封装是使这统统发挥浸染的关键推动成分。

让我们来看看苹果M1 - 一种经典的异构打算配置,特殊是其统一的内存构造。对我来说,M1的出身不是一个 "哗众取宠 "的时候,而是异构打算即将爆发的一个奇特时候。

M1正在敲响未来的样子,许多人很快就会效仿苹果的做法。请把稳,实际的SOC(片上系统)不是异构的--但是将内存靠近SOC的定制封装是异构的。

M1采取2.5D封装将内存直接封装到处理阁下,不须要PCB连线,

另一个非常好的高等封装的好例子是Nvidia的新款A100。再次把稳到PCB上没有电线。

HBM2 不像传统的 GDDR5 GPU 板设计那样须要环绕 GPU 的大量离散内存芯片,而是包括一个或多个多个内存芯片的垂直堆栈。存储芯片利用眇小的导线进行连接,这些导线由硅通孔和微突出形成。一个 8 Gb HBM2 芯片包含 5,000 多个硅通孔。然后利用无源硅中介层连接内存堆栈和GPU芯片。HBM2 堆栈、GPU 芯片和硅中介层的组合封装在单个 55mm x 55mm BGA 封装中。有关 GP100 和两个 HBM2 堆栈的图示,请拜会图 9;有关具有 GPU 和内存的实际 P100 的显微照片,请拜会图 10。

这里的结论是,天下上最好的芯片都是用一种办法制造出来的,而且这种革命不会停滞。接下来先容高等封装的两个紧张种别,2.5D和3D封装。

2.5D封装

2.5D有点像我们上面提到的倒装芯片的turbo版,但不是将单个裸片堆叠到PCB上,而是将裸片堆叠在单个中介层的顶部。我想这张图很好地解释了这一点。

2.5D就像有一个地下室的门进入你邻居的屋子,物理上是一个凸点或TSV(通过硅通孔)进入你下面的硅插板,这就把你和你的邻居连接起来。这并不比你实际的片上通信快,但由于你的净输出是由总的封装性能决定的,降落的间隔和增加的两个硅片之间的互连超过了没有在一个单一的SOC上的所有缺点。

这样做的好处是你可以利用 设计好的“小芯片”来快速拼凑更大更繁芜的封装。如果能在一块硅片上完造诣更好了,但这种工艺使制造变得更随意马虎,特殊是在较小的尺寸上。

“小芯片”和2.5D封装可能会利用很永劫光,它比3D封装更随意马虎制造,也便宜得多。此外,它可以很好地扩展,并且可以与新的小芯片一起重复利用,从而通过改换小芯片来制造相同封装格式的新芯片。AMD的新的Zen3改进便是这样的,个中封装相似,但一些小芯片得到了升级。

3D封装

3D封装是一个“圣杯”圣杯,是封装的终极闭幕。可以这样比喻,现在,与其在地面上拥有所有1层楼高并由地下室连接的独立小房子,不如拥有一座巨大的摩天算夜楼,该摩天算夜楼是用适宜功能所需的任何工艺定制的。这是3D封装 - 现在所有的封装都是在硅片本身上完成的。它是驱动更大、更繁芜构造的最快、最节能的方法,这些构造是为任务而构建的,并将显著延长摩尔定律。未来我们可能无法得到更多的芯片尺寸紧缩,但现在有了3D封装,我们仍旧可以在未来改进我们的芯片,类似于以前的摩尔定律。

而有趣的是,我们有一个全体半导体市场走向3D的明显例子--内存。存储器向3D构造的推进是对未来发展的一个很好的解释。NAND不得不采取3D构造的部分缘故原由是它们在较小的几何尺寸上难以扩展。想象一下,内存是一座大型的3D摩天算夜楼,每一层都由一个电梯连接起来。这些被称为 "TSV "或通硅孔。

这便是未来的样子,我们乃至有可能将GPU / CPU芯片堆叠在彼此上或在CPU上堆叠内存。这是末了的边陲,而现在我们正在迅速靠近的边陲。在接下来的5年里,你可能会开始看到3D封装一遍又一各处涌现。

2.5D/3D 封装办理方案快速概述

我认为,与其进一步理解3D和2.5D封装,不如直接先容一些正在利用的、你可能已经听说过的工艺。我想在这里重点谈谈晶圆厂所做的工艺,这些工艺是推动了3D/2.5D集成发展的。

台积电的CoWoS

这彷佛是 2.5D 集成工艺的主力,由 Xilinx 率先推出。

该过程紧张集中在将所有逻辑芯片放入硅中介层上,然后放到封装基板上。统统都通过微突出或球连接。这是一个经典的2.5D构造。

台积电SOIC

这个台积电的3D封装平台, 是一个相对较新的技能。。

把稳这个关于凸点密度和接合间距的惊人图表,SoIC在尺寸上乃至没有靠近Flipchip或2.5D,而是在密度和特色尺寸方面险些是一个前端工艺。

这是对他们技能的一个很好的比较,但请把稳,SoIC实际上有一个类似于3D堆叠的芯片堆叠,而不是中阶层2.5D集成。

三星 XCube

近年来,三星已成为更主要的代工厂互助伙伴,当然,为了不被超越,三星拥有了新的3D封装方案。不才面查看他们的XCube的视频。

这里没有太多的信息,但我想强调的是,A100是在三星工艺上制造的,以是这可能是为Nvidia最近的芯片供应动力的技能。此外,在这里所有的公司中,三星可能有最丰富的tsv履历。

英特尔 Foveros

末了是英特尔的Foveros 3D封装。我们可能会看到英特尔在未来7nm及往后的"稠浊CPU"工艺中实现更多。他们在架构日已经非常明确地表示,这是他们提高的重点。

有趣的是,在3D封装过程中,三星,台积电或英特尔之间并没有太大的差异。

原文:

https://semiwiki.com/semiconductor-services/308968-semiconductor-packaging-history-primer/