CL1,CL2为匹配电容,Rext常日为串联的几百欧姆电阻(有时也不加)。上面这个构造可能看着不是很熟习,我们把它转换一下,变成下面这个就熟习些。

上图中把RF忽略掉了,如果用过无源晶振的话,该当知道这个RF的阻值一样平常是很大的,兆欧姆级别,其浸染紧张是为了给反相放大器一个得当偏置。就像我们模电里面的三极管电路,其事情时都须要得当的直流偏置,这里我们先忽略掉。

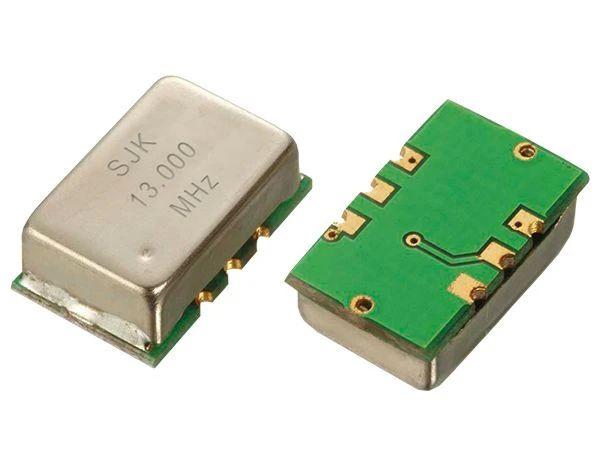

结合上一章节说的晶振的等效电路

我估计有人看到这里就跑了,这一坨是什么东西,搞这么繁芜?实在没那么难,这里面所有的器件,除了反相放大器外,都是基本元器件,反而是更随意马虎剖析的。不过在这之前呢?我们还是插播一个知识点,那便是起振条件。由于只有搞懂了起振条件,我们才能知其然并且知其以是然,先理论剖析,然后用仿真去验证,如此更爽。

起振条件起振条件有两个:相位和环路增益

上图中将反相放大器的通报函数用A(s)表示,晶振及其匹配电路打包一起,其通报函数看作F(s)。当环路增益大于1时,解释输入旗子暗记在环路中逛一圈后又送到输入端,旗子暗记幅度比原来更大相位为2nπ,说输入旗子暗记在电路中逛一圈后,相位与原来的输入旗子暗记完备相同,因此输入旗子暗记被完美的加强了。两者结合,就形成了这样的情形:旗子暗记经由反复放大后,不断增大,终极便是我们看到那样。当环路中的旗子暗记幅度增大到一定程度后,振荡器中的有源器件(晶振电路中的反相器)存在的非线性会限定幅度的连续增加,使得振荡器的输出达到稳定。普通说便是振荡的幅值肯定超不过电源电压。

也便是说,只要知足那两个条件,再小的旗子暗记,经由环路的无限循环(输入旗子暗记Vin逛一圈变成更大的Vin,然后再逛一圈变成更更大的Vin,然后再逛一圈。。。),终极输出幅度总会起来。只管我们没有专门供应对应频率的输入旗子暗记Vin,但是电路中总会有噪声,比如白噪声便是全频段的,虽然旗子暗记很小,但是由于电路的这个不断加强的特性,以是终极一定有输出旗子暗记。也便是说,起振是一定的。总之,起振要知足这两个条件:

关于晶振起振,有一个准则叫巴克毫森稳定性准则,想深入去看的同学可以去查查。

起振电路剖析

上期说完了起振条件,那我们连续剖析前面的电路,先看相位。

相位

相位须要知足2nπ,显然,n不可能即是0,即是零意外着完备没有相移,电路中有反相放大器,已经相移了π,也便是180°。以是最可能的便是晶振那一坨电路也让旗子暗记相移180度,整体凑够360°,也便是2π。

Rext和匹配电容CL1构成一个低通滤波器,带来的相移是小于90°的,这该当很随意马虎知道,下图是Rext=100Ω,CL1=10p的低通滤波器的幅频曲线,可以看到,输入与输出的相位差是:0°~90°,输出滞后输入。

Rext和匹配电容CL1带来的相移是小于90°,那么晶振与CL2带来的相移必须大于90°,如此才能凑够180°。 那么什么时候晶振与CL2带来的相移是大于90°的呢?答案是必须晶振等效电路整体呈电感性才有可能。

晶振等效电路有三种元器件构成,电阻,电感,电容,其总的等效阻抗可能有三种情形:呈阻性,呈容性,呈感性。如果从数学角度来看,晶振总阻抗公式化简之后总能写成一个复数的形式,包含实数和虚数的表达式:Z=R+jX。个中R是电阻分量,X为电抗分量。当X=0:Z=R,整体呈阻性当X>0:Z=R+jX,整体呈感性当X<0:Z=R+jX,整体呈容性。下面分别看下三种情形下,晶振与匹配电容CL2的相位情形。阻抗公式算出来肯定是一大坨的,就不列了,我们直接看仿真,这样更为直不雅观(电阻100只是象征性取值,可以取其它的,不影响结果,电容值也是)

可以看到,只有晶振在呈感性的时候,相移才能大于90°,其相移范围是:0~180°。综上所述,晶振事情时呈感性。那么,晶振呈感性的频率范围是多少呢? 晶振呈感性频率范围阻抗呈感性的频率范围,列出晶振的总阻抗公式就好了。

理论上说,总阻抗是个复数,我们可以把它化简成实部和虚部,虚部大于0时,即表示晶振呈感性。不过这也太费劲,还是直接搞一个实际的晶振参数看看。大多数晶振都是没有给出Lm,Rm,Cm参数的,不过我查到爱普生的晶振有写出来,比如下面这款25Mhz的晶振。

可以看到,Rm最大为80Ω,动态电容Cm=1.94fF,动态电感Lm=20.91mH,静态电容C0=0.6pF。我们直接用这些参数,采取LTspice仿真的办法画出阻抗曲线吧。

仿真的事理很大略,给一个1A的电流源,那么Vz的电压便是阻抗乘以电流,电流为1A,那么Vz的值便是阻抗值,因此,图中左边的dB幅度值便是阻抗值。相位表示电压超前电流的相角,因此,如果相位大于0,表示整体阻抗是感性,若小于0,表示整体阻抗是容性的。从图中可以看出,两个尖之间的区域,相角大于0,便是呈感性的区域,晶体振荡频率25Mhz正好处于这一区域。

从图上看,两个冒尖的频率分别是24.988623Mhz,25.028984Mhz,很随意马虎猜到,两个冒尖的频点这么分外,该当是串联谐振点和并联谐振点。我们可以验证下,分别打算下串联谐振和并联谐振。

打算值fs=24.988619Mhz,仿真图读值fs=24.988623Mhz打算值fa=25.0289844Mhz,仿真图读值fa=25.028984Mhz可以看到,可以说完备同等。因此,晶体事情频率范围为:

当 然,以上只是说晶振实际事情的频率处于这个之间,并不是说实际事情时频率变革范围有这么大,衡量稳定度是有个参数叫频偏,把稳不要误解。 小结本节就写到这里了,暂时只解释了相位关系,实在还有些问题没搞清楚。比如这个:我们都知道实际运用中,改变匹配电容,可以微调晶振事情频率,以是实际事情频率跟匹配电容肯定有关系,该当是有关系式的。详细关系式我在一些资料中已经看到了,不过只知道个结果吧,还没搞清楚咋来的,暂时就先放着吧。以上便是本期内容了,如果有问题,欢迎留言指出。

"大众年夜众号:硬件工程师炼成之路