1.2万亿个晶体管,一片12英寸晶圆仅能做一颗芯片,史上最大芯片出身!

专门面向AI任务!

这颗巨型芯片,面积42225 平方毫米,拥有1.2 万亿个晶体管,400000 个核心,片上内存18G字节,内存带宽19PByte/s,fabric带宽100Pbit/s。是目前芯片面积最大的英伟达GPU的56.7倍!

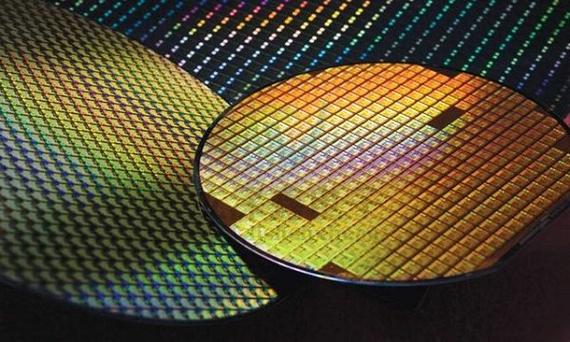

一块12英寸晶圆仅做一颗芯片

是目前芯片面积最大的英伟达GPU的56.7倍!

这便是有史以来最大的芯片——Cerebras Wafer Scale Engine!

是由人工智能初创公司Cerebras Systems公司推出,拥有1.2万亿个晶体管。1971年英特尔首款4004处理器拥有2,300个晶体管,最近的Advanced Micro Devices处理器拥有320亿个晶体管。

大多数芯片实际上是在12英寸硅晶圆片上创建的芯片凑集,每块硅晶圆片可以集成成百上千颗芯片。但Cerebras Systems芯片是在单个晶圆上互连的单芯片。这些互连设计使其全部保持高速运行,因此万亿个晶体管全部一起事情。

通过这种办法,Cerebras Wafer Scale Engine是有史以来最大的处理器,它专门设计用于处理人工智能运用。该公司本周正在加利福尼亚州帕洛阿尔托的斯坦福大学举行的Hot Chips会议上谈论这项设计。

三星实际上已经制造了一个闪存芯片,即eUFS,拥有2万亿个晶体管。但Cerebras芯片专为加工而设计,拥有400,000个核心,42,225平方毫米。它比最大的Nvidia图形处理单元大 56.7倍,该单元的尺寸为815平方毫米和211亿个晶体管。

WSE还包含3,000倍的高速片上存储器,并且具有10,000倍的存储器带宽。

该芯片来自Andrew Feldman领导的团队,后者曾创建微型做事器公司SeaMicro,并以3.34亿美元的价格出售给Advanced Micro Devices。Cerebras Systems的联合创始人兼首席硬件架构师Sean Lie将概述热芯片上的Cerebras Wafer Scale Engine。加利福尼亚州Los Altos公司拥有194名员工。

安德鲁费尔德曼与原始的SeaMicro盒子。

芯片尺寸在AI中非常主要,由于大芯片可以更快地处理信息,在更短的韶光内产生答案。减少洞察韶光或“培训韶光”,使研究职员能够测试更多想法,利用更多数据并办理新问题。谷歌,Facebook,OpenAI,腾讯,百度和许多其他人认为,本日人工智能的基本限定是培训模型须要很永劫光。因此,缩短培训韶光肃清了全体行业进步的紧张瓶颈。

当然,芯片制造商常日不会制造这么大的芯片。在单个晶片的制造过程中常日会涌现一些杂质。如果一种杂质会导致一块芯片发生故障,实际制造出的芯片产量有一定良率,不可能100%都能用。但Cerebras设计的芯片留有冗余,一种杂质不会导致全体芯片都不能用。

性能上风及用场一个芯片供应超级打算机级的打算能力“Cerebras WSE”专为人工智能设计而设计,个中包含了不少根本创新,办理了限定芯片尺寸的长达数十年的技能寻衅 - 如芯片良率,功率传送、封装等,推动了最前辈技能的发展。和包装,每个架构决策都是为了优化AI事情的性能。结果是,Cerebras WSE根据事情量供应了数百或数千倍的现有办理方案的性能,只需很小的功耗和空间。”Cerebras Systems首席实行官的Fieldman说。

通过加速神经网络演习的所有元向来实现这些性能提升。神经网络是一种多级打算反馈回路。输入在循环中移动速率越快,循环学习的速率越快,即演习韶光越短。可以通过加速循环内的打算和通信来加速输入的循环速率。

Linley Group首席剖析师Linley Gwennap在一份声明中说:“Cerebras凭借其晶圆级技能实现了巨大的飞跃,在单片硅片上实现了比任何人想象的更多的处理性能。为了实现这一壮举,该公司已经办理了一系列恶性工程寻衅,这些寻衅几十年来阻碍了该行业,包括履行高速芯片到芯片通信,办理制造毛病,封装如此大的芯片,以及供应高本钱 - 密度电源和冷却。通过将各种学科的顶级工程师聚拢在一起,Cerebras在短短几年内创造了新技能并交付了一个产品,这是一项令人印象深刻的造诣。”

Cerebras WSE芯片面积比目前最大的GPU大56.7倍, 并供应更多核心进行打算,有更多核心靠近内存,因此内核可以高效运行。由于这些大量的内核和内存位于单个芯片上,因此所有通信都在芯片上进行,通信带宽高、延迟低,因此核心组可以以最高效率进行协作。

Cerebras WSE中的46,225平方毫米的芯片面积上包含40万个AI优化核心,无缓存、无开销的打算内核,以及18G字节确当地化分布式超高速SRAM内存。内存带宽为每秒9PB(9000TB)。这些核心通过细粒度、全硬件、片上网络连接在一起,可供应每秒100Pb(1001000Tb)的总带宽。更多核心、更多本地内存和低延迟高带宽构造,共同构成了面向AI加速任务的最佳架构。

“虽然AI在一样平常意义上被利用,但没有两个数据集或两个AI任务是相同的。新的AI事情负载不断呈现,数据集也在不断变大,”Tirias Research首席剖析师兼创始人Jim McGregor在一份声明中表示。

“随着AI的发展,芯片和平台办理方案也在不断发展。Cerebras WSE是半导体和平台设计方面的一项惊人的工程造诣,它在单个晶圆级的办理方案中供应了超级打算机级的打算能力、高性能内存和带宽。”

Cerebras 表示,如果没有多年来与台积电(TSMC)的密切互助,他们不可能取得这个创记录的造诣。台积电是环球最大的半导体代工厂,在前辈工艺技能方面处于领先地位。WSE芯片由台积电采取前辈的16nm制程技能制造。

更加深入的学习打算WSE包含400,000个AI优化的打算核心。被称为稀疏线性代数核心的SLAC,打算核心灵巧,可编程,并针对支持所有神经网络打算的稀疏线性代数进行了优化。SLAC的可编程性确保内核可以在不断变革的机器学习领域中运行所有神经网络算法。

由于稀疏线性代数核心针对神经网络打算基元进行了优化,因此它们可实现业界最佳利用率 - 常日是图形处理单元的三倍或四倍。此外,WSE核心包括Cerebras发明的稀疏性网络技能,以加速稀疏事情负载(包含零的事情负载)的打算性能,如深度学习。

WSE包含40万个AI优化的打算内核(compute cores)。这种打算内核被称为稀疏线性代数核(Sparse Linear Algebra Cores, SLAC),具有灵巧性、可编程性,并针对支持所有神经网络打算的稀疏线性代数进行了优化。SLAC的可编程性担保了内核能够在不断变革的机器学习领域运行所有的神经网络算法。

由于稀疏线性代数内核是为神经网络打算进行优化的,因此它们可实现业界最佳利用率——常日是GPU的3倍或4倍。此外,WSE核心还包括Cerebras发明的稀疏捕获技能,以加速在稀疏事情负载(包含0的事情负载)上的打算性能,比如深度学习。

零在深度学习打算中很普遍。常日,要相乘的向量和矩阵中的大多数元素都是0。然而,乘以0是摧残浪费蹂躏硅,功率和韶光的行为,由于没有新的信息。

由于GPU和TPU是密集的实行引擎——引擎的设计永久不会碰着0——以是它们纵然在0时也会乘以每一个元素。当50-98%的数据为零时,如深度学习中常常涌现的情形一样,大多数乘法都被摧残浪费蹂躏了。由于Cerebras的稀疏线性代数核心永久不会乘以零,所有的零数据都被过滤掉,可以在硬件中跳过,从而可以在其位置上完成有用的事情。

高效,高性能的片上存储器-比GPU大3000倍内存是每一种打算机体系构造的关键组成部分。靠近打算的内存意味着更快的打算、更低的延迟和更好的数据移动效率。高性能的深度学习须要大量的打算和频繁的数据访问。这就哀求打算核心和内存之间要非常靠近,而在GPU中却不是这样,GPU中绝大多数内存都很慢,而且离打算核心很远。

Cerebras Wafer Scale Engine包含了比迄今为止任何芯片都要多的内核和本地内存,并且在一个时钟周期内拥有18GB的片上内存。WSE上的核心本地内存的凑集供应了每秒9PB的内存带宽——比最好的GPU大3000倍的片上内存和10000倍的内存带宽。

带宽,低延迟通信构造Swarm通信构造是WSE上利用的处理器间通信构造,它以传统通信技能功耗的一小部分实现了带宽的打破和低延迟。Swarm供应了一个低延迟、高带宽的2D网格,它将WSE上的所有400,000个核连接起来,每秒的带宽总计达100 petabits。

路由、可靠的通报和同步都在硬件中处理。会自动激活每个到达的运用程序处理程序。Swarm为每个神经网络供应了一个独特的、优化的通信路径。软件根据正在运行的特定用户定义的神经网络的构造,配置通过400,000个核心的最优通信路径,以连接处理器。

范例的通过一个具有纳秒延迟的硬件链接。一个大脑WSE的总带宽是每秒100 pb。不须要TCP/IP和MPI等通信软件,因此可以避免性能丢失。这种构造的通信能量本钱远低于1皮焦耳每比特,这比图形处理单元低了近两个数量级。结合了巨大的带宽和极低的延迟,群通信构造使大脑WSE比任何当前可用的办理方案学习得更快。

原文链接:

https://venturebeat.com/2019/08/19/cerebras-systems-unveils-a-record-1-2-trillion-transistor-chip-for-ai/amp/?from=timeline.