传感器专家网https://www.sensorexpert.com.cn

专注于传感器技能领域,致力于对环球前沿市场动态、技能趋势与产品选型进行专业垂直的做事,是海内领先的传感器产品查询与媒体信息做事平台。基于传感器产品与技能,对广大电子制造从业者与传感器制造者供应精准的匹配与对接。

半导体 MEMS 的主要性

MEMS 紧张是传感器系统,可以掌握或感测化学、光学或物理量,例如流体、加速度或辐射。MEMS 设备/传感器拥有与外界的电气接口,常日通过 IC 实现,IC 供应必要的智能,使设备能够实行有用的功能。

例如,IC 可以供应系统测试功能、逻辑和通信功能以及模数转换等旗子暗记调节功能。IC和MEMS可以利用两种方法集成,包括稠浊多芯片集成/多芯片办理方案和片上系统(SoC)集成/SoC办理方案。

在传统的多芯片办理方案方法中,IC 和 MEMS 元件最初是利用专用 IC 和 MEMS 制造工艺在单独的基板上合成的,然后在终极系统中稠浊,而在最近的 SoC 办理方案方法中,IC 和 MEMS 元件是制造的利用交错或连续处理方案在同一基板上进行。

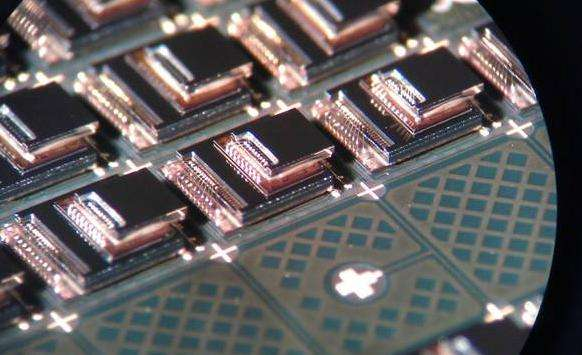

近几十年来,二维 (2D) 集成方法已广泛用于 MEMS 和 IC 技能的稠浊集成。在这些方法中,MEMS 和 IC 晶圆是独立设计、制造和测试的,然后分身分立的芯片。随后将分立芯片集成到封装或板级的多芯片系统中。

目前,大约一半的 MEMS 产品,包括多种微流体器件、射频 (RF) MEMS、压力传感器、麦克风、陀螺仪和加速计,均采取多芯片办理方案实现,而别的 MEMS 产品,包括喷墨打印头,红外测辐射热计阵列、数字镜器件以及许多压力传感器、加速度计和陀螺仪均作为 SoC 办理方案实现。

多种半导体 MEMS 产品由大型换能器阵列组成,个中每个换能器均单独运行,这些产品紧张作为 SoC 办理方案实现,以将每个 MEMS 换能器及其干系 IC 集成在单个芯片上。

通过稠浊集成的半导体 MEMS

传统上,IC和MEMS芯片是分开封装的,然后作为一个别系集成在印刷电路板(PCB)上,这导致了多芯片模块的发展。在半导体 MEMS 多芯片模块中,IC 和 MEMS 芯片并排放置在同一封装中,并在封装级利用引线和/或倒装芯片接合进行互连。

通过倒装芯片接合的多种 MEMS 和 IC 集成观点可用于多种运用,例如微光机电系统、MEMS 传感器和 RF-MEMS。最近的芯片到封装和芯片到芯片互连的观点,例如扇出晶圆级封装观点,是基于利用嵌入式芯片之间的薄膜互连而开拓的。

其他芯片到芯片互连方法包括绗缝封装,个中具有各种功能的芯片紧密地平铺在封装基板上,并利用从每个芯片突出的垂直面和机器柔性互连进行互连。

与板载系统方法比较,多芯片模块占用的 PCB 面积更小,并且芯片之间的旗子暗记路径长度显著缩短。因此,这个观点广泛运用于研究和商业产品中。

详细而言,MEMS 芯片与商用专用集成电路 (ASIC) 的集成可实现稠浊半导体 MEMS 系统的快速、大略且经济高效的履行。

系统级封装/垂直或堆叠多芯片模块由垂直连接的芯片组成,并利用导线和/或倒装芯片直接或通过额外的重新分布层互连。

与多芯片模块比较,更小的封装尺寸/体积、更短的旗子暗记路径长度和更高的集成密度是这些三维 (3D) 堆叠方法的紧张优点,这些方法用于压力传感器等商业产品。

晶圆级封装和芯片级封装观点可以产生高度紧凑的封装,其占用面积与封装中涉及的最大芯片尺寸相似。MEMS 芯片技能是这种方法的突出例子之一。

系统级封装方法可在封装级别实现小型化和高度集成的系统技能。在这些方法中,MEMS 和 IC 器件与其他几种基本技能(从电力电子和光学到无线组件)集成在一个通用封装中。

因此,低制造繁芜性、模块化和高灵巧性是多芯片办理方案的紧张优点,而厚度、大系统占用空间和有限的集成密度是紧张缺陷。

通过晶圆级集成的半导体 MEMS

SoC办理方案可分为单片MEMS和IC集成技能,个中IC和MEMS构造完备制造在同一基板上,以及异构MEMS和IC集成技能,个中IC和MEMS构造部分或全部预制在同一基板上。分离基板,然后合并到单个基板上。

利用单片 MEMS 和 IC 集成的 SoC 办理方案

在利用 MEMS 优先处理的单片 MEMS 和 IC 集成中,完全 MEMS 器件所需的所有处理步骤都在互补金属氧化物半导体 (CMOS) 处理之前实行,以实现后续 CMOS 集成并制造半导体 MEMS。

这些方法供应了有利的 MEMS 制造条件,例如极高的热预算,从而可以制造高性能 MEMS 构造,例如高性能 MEMS 谐振器。然而,预处理的 MEMS 晶圆的材料暴露和严格的表面平坦度哀求是紧张缺陷。

通过利用交错式 MEMS 和 IC 处理的单片 MEMS 和 IC 集成,半导体 MEMS 是通过在 CMOS 制造之后、期间或之前实行的 MEMS 处理步骤的组合来实现的。

只管这些方法许可将高性能 MEMS 器件和材料与 CMOS 电路集成在同一基板上,但它们须要完备访问专用的定制 CMOS 生产线,这极大地限定了该技能的普遍适用性。

在通过体微机器加工利用 MEMS 末了处理的单片 MEMS 和 IC 集成中,MEMS 构造是在全体 CMOS 制造工艺完成后制造的。

这种方法可以利用现有的 IC 根本举动步伐来实现,这是一个紧张上风。然而,CMOS 工艺所许可的 MEMS 器件的材料选择有限和设计自由度有限是紧张缺陷。

半导体 MEMS 可以通过单片 MEMS 和 IC 集成来实现,利用 MEMS 末了处理,通过表面微加工和层沉积。在这种方法中,MEMS 构造是通过微加工并在完全的 CMOS 晶圆上沉积材料来制造的。

虽然标准 CMOS 代工厂可用于这种方法中的 CMOS 晶圆制造,但 MEMS 材料的沉积温度必须保持在许可的 CMOS 晶圆温度预算/400-450 °C 之内,这使得该技能不适宜利用高温度实现的 MEMS 器件。-高性能MEMS材料。

利用异构 MEMS 和 IC 集成的 SoC 办理方案

异构 MEMS 和 IC 集成是指将两个或多个包含部分或完备制造的 MEMS 和 IC 构造的基板连接起来,以制造异构 SoC 办理方案。

层转移/先通孔工艺期间的异质 MEMS 和 IC 集成通孔形成许可将高性能 MEMS 材料与基于标准 CMOS 的 IC 晶圆集成。然而,它们常日须要对齐的基板到基板键合,这增加了工艺繁芜性并导致可实现的键合后对齐精度受到限定。