他所提到的美国牵制新规草案,是指10月7日,美国商务部家当安全局最新出台的对华半导体出口限定方法,个中紧张内容包括对18纳米或以下的DRAM芯片、128层或以上的NAND闪存芯片和14纳米或以下的逻辑芯片的出口,增加新的容许证哀求并严格审查,限定美国职员在没有容许证的情形下支持位于中国的某些半导系统编制造举动步伐集成电路开拓或生产的能力。

面对美国“卡脖子”方法的不断升级,通过Chiplet模式实现国产半导体家当的“弯道超车”开始逐步成为市场中的热议话题,也在A股中催化出了Chiplet观点板块,将这一陌生的名词带到了成本市场的投资者面前。

“Chiplet模式,可以将多个采取低工艺制程的模块,比如22nm工艺的模块拼装在一起,从而达到7nm工艺芯片的性能,使得厂商可以绕开前辈制程工艺的限定。”李振表示。

Chiplet是什么?

1965年,英特尔创始人戈登·摩尔总结了一个趋势,即集成电路上可以容纳的晶体管数目在大约每经由18个月到24个月便会增加一倍,性能也将提升一倍,同时其价格也会降落为原来的一半。

这一原来是摩尔等业内人士的履历之谈,在经由归纳后便逐渐成了影响半导体行业发展至今的摩尔定律。

“摩尔定律并非自然规律,该当被视为对集成电路性能发展的不雅观测或预测。过去半个多世纪以来,半导体行业大致按照摩尔定律发展。”灼识咨询合资人赵晓马向阐明。

但眼下,随着芯片制造工艺的不断发展,按照摩尔定律提高晶体管密度以提升芯片性能的方法,也逐渐碰着了瓶颈。

“单个芯片上集成的晶体管数量从几千个增加到十几亿个,受制于芯片尺寸的物理极限、光刻技能、隧道效应、功耗和散热、供电能力等问题,制造工艺从5nm升级到3nm再到2nm,其间隔都超过了2年韶光。”赵晓马进一步指出,

面临摩尔定律发展趋缓,开拓前辈制程的本钱及研发难度不断提升的现状,半导体行业开始拓展新的技能路线试图延续摩尔定律,而如今被视为“救命稻草”的Chiplet观点也由此提出。

赵晓马见告,在后摩尔时期,新集成、新材料、新架构成为行业创新的焦点。而在新集成中,就包括Chiplet和前辈封装,Chiplet由于其高性能、低功耗、高面积利用率以及低本钱受到广泛关注,在FPGA(可编程器件)、GPU(图形处理器)等高性能打算市场具备很高潜力。

“Chiplet,实质上是一个设计理念,它将不同工艺、不同功能的模块化芯片,通过封装和互联等办法,像拼接乐高积木一样用封装技能整合在一起,形成一颗芯片。大略来说,Chiplet是小芯片或者说芯粒在封装层面整合的办理方案。”上海奎芯科技产品副总裁王晓阳在接管经济不雅观察网采访时表示。

赵晓马认为,Chiplet最大的特点便是从系统的角度来延续“摩尔定律”的经济效益,器件将以多种办法集成,系统空间内的功能密度将持续增长。

“首先,Chiplet可供应较大的性能功耗优化空间,支持面向特定领域的灵巧定制。其次,有效提升旗子暗记传输质量和带宽。第三,利用小芯片(具有相对低的面积开销)低工艺和高良率的特性,可以有效降落本钱。第四,可以有效缩短芯片的研发周期及节省研发投入,并降落研制风险。”赵晓马补充说。

在王晓阳眼中,Chiplet作为一条超过摩尔定律的技能路径,对家当链上IP(可复用设计模块)公司、前辈封装公司、晶圆公司来说,不亚于是一次革命性的改变。

“以前的SoC(系统级芯片)设计方法学中IP已经设计成可以复用的,但是形成SoC原型设计往后该走的软硬件协同验证、后端与物理设计、流片制造的流程一个也少不了。”王晓阳见告。

“如果是Chiplet的话,只须要直接做一次封装加工就可以用起来,其复用程度远超过现在的IP。”他进一步阐明。

Chiplet模式所具有的诸多上风,让各种芯片厂商纷纭加快自身在这一领域的技能布局。

就在今年3月,包括英特尔、AMD、台积电在内的10家集成电路领域的头部厂商发起成立了UCIe家当同盟 (Universal Chiplet Interconnect Express) ,旨在进一步加速Chiplet生态的发展,制订行业间的互联标准,个中也包括多家中国大陆半导体公司,例如芯原股份、芯和半导体、长电科技、灿芯半导体等。

据市场研究机构Omdia测算,2021年环球Chiplet市场规模已达到18.5亿美元,估量未来五年仍将以46%的年均复合增长率高速增长,到2035年环球Chiplet市场规模或将超过570亿美元。

国产IP设计家当受益

“目前在布局Chiplet领域的A股上市公司有两类,分别是IP设计公司、前辈封装与封测设备公司。个中,IP设计领域的代表公司是芯原股份(688521.SH),封装领域的代表公司有通富微电(002156.SZ)及长电科技(600584.SH)。”沪上一家大型券商的电子首席剖析师王泓见告经济不雅观察网。

理解到,Chiplet实质上是一种异构集成,即将不同制程、不同性子的芯片整合在一起,由此也给芯片产品带来了三大寻衅,分别是:芯片带宽不一致导致的旗子暗记传输不稳定、Chiplet互连不直接导致的功耗不平衡、Chiplet的堆叠导致的散热问题。

“前辈封装是办理Chiplet异构集成的关键办法,目前行业内紧张的前辈封装工艺有倒装封装、晶圆级封装、2.5D/3D封装以及系统级封装等,尤其后三者是行业焦点。“赵晓马指出。

作为封测领域领军企业的通富微电在今年的半年报中,曾表露表示:“公司通过在多芯片组件、集成扇出封装(晶圆级封装的一种形式)、2.5D/3D 等前辈封装技能方面的提前布局,可为客户供应多样化的 Chiplet封装办理方案,并且已为AMD大规模量产 Chiplet 产品。”

长电科技也在9月25日于上证e互动回答投资者称:“得益于集团全资子公司星科金朋在Chiplet 干系技能领域积累的长期量产履历和大量专利,公司目前拥有用于Chiplet封装的超大尺寸FCBGA(倒装芯片封装)封装技能能力,多层芯片超薄堆叠及互联技能能力,与极高密度多维扇出型(一种降落尺寸与本钱的封装工艺)异构集成技能能力,正在持续推进该技能的生产运用和客户产品的导入。”

而在早前4月份的一场网络调研中,长电科技方面就曾表示,公司2021年前辈封装包括除打线与测试外的其他封装形式,收入占比已达60%以上。

不过,从上述两家公司的财务表现看,前辈封装的运用,尚未改变其营收规模较小、盈利能力较弱的现状。

根据长电科技2022年半年报表露,2022年1月份至6月份,长电科技实现业务收入155.94亿元,同比增长12.85%;实现扣非净利润仅14.09亿元,同比增长50.14%,这一数据比较去年同期217.62%的增速水平已是大幅放缓。

而通富微电的情形则更不乐不雅观,该公司今年上半年实现业务收入95.67亿元,同比增长34.95%;实现扣非净利润仅3.65亿元,同比低落14.23%。

对付盈利水平的低落,通富微电在半年报中归结于“受汇率颠簸影响”。

“由于技能含量较低,对付封测行业,盈利能力较弱一贯是个绕不开的话题,但从长期来看,前辈封装有望改变这一现状,随着Chiplet技能的持续落地,前辈封装有望给行业内公司供应充足发展动能。”王泓见告。

此外,王泓指出,相较于封测领域,国产IP设计家当在Chiplet的快速发展中受益会更多。

所谓芯片IP,即指芯片中预先设计、验证好的功能模块,这些模块在芯片设计过程中可被反复利用,因此,业内也有不雅观点将Chiplet技能称为不同芯片IP间的组合。

“打个形象地比喻,芯片设计公司须要做满汉全席,而IP就可以算作是一道菜的菜谱,见告他这道菜该怎么做,而Chiplet则可以算作是这道菜的预制菜,芯片设计公司仅须要大略加热即可上桌。”王晓阳见告。

“比如我们是做高速互联的IP,可以供应给芯片设计公司,我们既可以发卖IP的办法(菜谱),也可以把IP做成Chiplet产品硬件化(预制菜),供应给客户。”他进一步向阐明说。

赵晓马指出,传统单片系统设计办法是从不同的IP供应商处购买IP,结合自研模块集成,而在Chiplet模式下只须要购买供应商生产好的Chiplet小芯片,将其封装形成系统芯片即可。

“Chiplet是新的硅片级IP重用模式,在工艺选择、架构设计上都具有灵巧性,优化了IP硬核(已成型的功能模块)无法修正导致的复用困难和利用范围较窄的问题。”他剖析称。

王晓阳见告经济不雅观察网,其所在公司的IP产品已经成功在一些有名厂商的7纳米以上工艺节点得到验证并实现量产,目前产品已能涵盖从12nm到180nm的根本库IP,7nm到110nm的接口类IP,以及仿照IP和定制服务。

“目前我们的研发团队﹐正在集中力量自主研发14/12纳米及以下的前辈工艺IP。”王晓阳进一步补充说。

李振则见告,目前数据中央、汽车电子及电脑处理器三大领域是Chiplet技能的主流运用方向。

“Chiplet的车规级产品落地较快,国产的GPU(图形处理器)、NPU(神经处理单元)、ISP(图像旗子暗记处理器)等IP产品已经被广泛运用于车载系统当中,比如赞助驾驶模块,车载大屏等等。”李振说,

王晓阳亦表示,随着汽车家当智能化和网联化程度的不断提高,汽车自动驾驶和智能座舱采取了繁芜的SOC芯片,打算/感知/实行都须要更快的数据传输能力给予支撑,而Chiplet可以大幅简化汽车芯片迭代时的设计事情和车规流程,同时增加汽车芯片的可靠性。

国产IP行业的龙头芯原股份在2022年的半年报等分析称:“在汽车‘缺芯’潮的背景下,大众、福特、通用、北汽、比亚迪等传统汽车制造企业和特斯拉、小鹏、蔚来、空想、零跑等新能源汽车厂商纷纭表示将要自主设计汽车芯片,这种趋势为集成电路设计家傍边半导体 IP 和芯片设计做事的发展扩展了市场空间。”

根据行业研究机构Statista的数据显示,2020 年环球汽车电子市场规模约为2180亿美元,到2028年有望达到4000多亿美元,增长逾80%,年复合增长8%旁边。

但值得把稳的是,目前在IP设计领域也依旧存在“卡脖子”的征象。

“目前环球紧张的IP供应商来自英美,尤其是在高速互联IP,高端CPU、GPU等核心IP领域,国际大厂已经形成了较高的技能壁垒。海内IP企业虽然正在向国际领先IP厂商全面追赶,但行业整体底子还较为薄弱。”王晓阳见告。

他指出,目前在IP领域的国产化率还比较低,在高速接口IP,高端GPU/CPU IP领域的国产化进程仍处于起步阶段。外洋芯片巨子在Chiplet领域也较为领先。

在他看来,近几年海内芯片设计的水平进步十分显著,但更多还局限在“如何把芯片设计完成并落地”。

“IP设计属于家当链上游,所要办理的是工程问题而不是科学问题,而工程问题须要家当链高下游进行磨合,须要客户帮助创造、办理问题,以进行迭代。以是,国产IP只要有机会去不断考试测验、打破,是非常有机会赶超的。”王晓阳进一步补充说,

绕不开的前辈制程

10月7日,美国商务部家当安全局(BIS)再度出台了对华半导体出口限定方法,旨在进一步限定海内得到前辈打算芯片、开拓和掩护超级打算机以及制造前辈半导体的能力。

在美国商务部家当安全局官网上,经济不雅观察网梳理了这份牵制新规的紧张内容,个中,BIS表示,将对目的地为中国的半导系统编制造举动步伐且能制造符合特定标准的集成电路之物项,增加新的容许证哀求,容许证的干系阈值如下:非平面晶体管构造16nm或14nm或以下(即FinFET或GAAFET)的逻辑芯片半间距18nm或以下的DRAM存储芯片;128层或以上的NAND闪存芯片。

此外,还把稳到有一项条款,将限定美国职员在没有容许证的情形下支持位于中国的某些半导系统编制造举动步伐集成电路开拓或生产的能力。

“其实在10月以前,圈内就陆续有美国要加码制裁的传闻了,但是在真的看到条款内容时,我还是很惊异,这是一次全方位的封杀,我们学校一些学弟都跑来咨询我情形怎么样,要不要转专业。”李振在电话中见告。

而在美国持续加码限定中国半导体家当的背景下,通过Chiplet技能能绕开前辈制程限定的不雅观点开始风靡于市场中。

“这种不雅观点大存问思是,将多个采取低工艺制程的模块,比如22nm工艺的模块拼装在一起,从而达到7nm工艺芯片的性能。”李振说。

在李振看来,这样的做法逻辑上确实可行,也已有部分厂商采纳了此类方案,但该方案在经济效益上却存在一定问题。

“这种方案只能说应急,但绝不是正道,用低工艺攒出来的产品,只能说靠近前辈制程芯片的部分性能,不可能完备达到同等性能,还会带来本钱的上升。”他说,

王泓亦向表示,这种“曲线救芯”的办法,实质上是通过偏封装层面的技能实现,但底层制造工艺才是决定芯片性能上限的核心要素。

“光靠Chiplet没办法超车,而且在Chiplet领域我们也不领先,你可以通过几个14纳米模块的联系把性能往上提一提,但在同等面积下,肯定是比不过7nm的,前辈制程是绕不开的,以是美国现在完备不让你买前辈制程的产品,确实给家当带来不小的麻烦。“王泓说。

他认为,中国大陆的半导体行业,通过Chiplet实现弯道超车,绕开前辈制程的说法,更像是一种感情的开释,“最近的市场太须要一些好了。”

赵晓马也见告,Chiplet模式的涌现背后是摩尔定律越来越靠近极限,在这样的背景下,半导体的技能进步比原来更难也更慢了,这本身对付海内半导体家当的追赶是一个好。而Chiplet这个技能通过前辈封装来实现,不须要光刻机,这对付企业而言也是好。

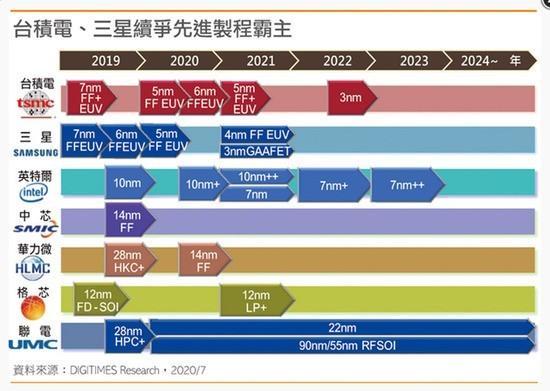

“除了好外,我们也要看到,目前Chiplet这块的竞争者是原来的顶级晶圆厂,台积电、三星和英特尔,他们也各自有核心技能的积累,例如台积电的Hybrid Bonding技能,难度极高。”赵晓马向经济不雅观察网表示。

(应受访者哀求,文中王泓为化名)