封测设备包括封装设备与测试设备。封装设备方面,紧张包括与引线键合工艺中背面减薄、晶圆切割、贴片、引线键合、模塑密封、切筋成型六大工序相对应,传统封装设备按工艺流程紧张分为减薄机、划片机、贴片机、引线键合机、塑封机及切筋成型机。在以凸点焊Bumping代替引线键合的前辈封装工艺中,还需用到倒装机、植球机、回流炉等设备。此外,如硅通孔TSV等前辈封装工艺中也会用到光刻机、刻蚀机、电镀机、PVD、CVD等。测试设备方面,则是指用于后道封测环节的检测设备,根据功能的不同包括分选机、测试机、探针台。

1、封装设备:封装行业精度、技能门槛高,设备精度哀求在微米级别。由于芯片良品率会导致生产本钱的差异,半导体设备所能供应的良率将直接影响上层产品的盈利能力。根据思摩尔公司的测算,当良品率从85%提高至90%,毛利率将增加9.06%,当良品率进一步从85%增加至95%,对应的毛利率将增加17.3%。我们将紧张的封装设备总结为下表:

(1)传统封装设备

贴片机(Die bonder),也称固晶机,是封测的芯片贴装(Die attach)环节中最关键、最核心的设备。其功能紧张是将芯片从已经切割好的晶圆(Wafer)上抓取下来,并安置在基板对应的Die flag上,利用银胶(Epoxy)把芯片和基板粘接起来。贴片机可高速、高精度地贴放元器件,并实现定位、对准、倒装、连续贴装等关键步骤。无论封装办法如何演化,封装过程都离不开贴装过程。随着芯片小型化的需求,哀求贴片机的精度范围在3~5微米之间。为了达到风雅化的贴装,封装厂的前辈封装产线对贴片机的精度、速率、良品率、稳定性的哀求都非常高,在前辈封装过程中贴片机是最关键、最核心的设备。

贴片机可按照运用的不同分为前辈封装设备(包括FC封装贴片机、FO封装贴片机和2.5D/3D贴片机)和传统封装设备(包括传统封装贴片机和叠层封装贴片机)。传统封装贴片机的生产速率可达到15千个每小时,叠层封装可达到2千个每小时,前辈封装中FC封装贴片机可达8千个每小时,FO封装贴片机可达6千个每小时,而2.5D/3D贴片机则为2千个每小时。由于FC倒装设备是否属于前辈封装在业内存在争议,因此晶圆级封装的贴片机是前辈封装设备的最范例代表。

划片机,按晶圆上的划片街区(晶圆上的芯片之间留有80um至150um的间隙,此间隙被称之为划片街区)将每一个具有独立电气性能的芯片通过切割分离出来。晶圆划片紧张有刀轮切割和激光切割两种,目前刀轮切割霸占主流路线。镭射切割紧张运用于逻辑芯片,掌握芯片等高技能哀求的芯片,占比约为15到20%,刀片切割则运用于别的的低技能哀求芯片中。划片机的生产速率根据统计均匀约为6千个每小时。

键合机,又称引线机,利用金属丝(金线、铜线、铝线等),利用热压或者超声能源,完成芯片与电路或引线框架之间的连接。按照工艺技能,键合分为球形焊接(ball bonding)和楔形焊接(wedge bonding);按照焊接事理分为热压焊、超声波焊、热超声波焊。大部分引线机焊接速率在每秒24根引线。紧张运用于大功率器件、MOSFET、IGBT、发光二极管(LED)、激光管(激光)、中小型功率三极管、集成电路和一些分外半导体器件的内引线焊接。由于倒装技能的发展不再须要引线,因此引线机的市场份额会随着前辈封装时期的发展而低落。

晶圆减薄机,紧张用于晶圆的背面减薄工艺中。晶圆减薄的紧张工序为首先在正面(Active Area)贴胶带保护电路区域,同时研磨背面。研磨之后,去除胶带,丈量厚度。个中,磨削包括粗磨、精磨和抛光三个阶段。

塑封设备可以将芯片可靠地封装到一定的塑料外壳内。塑封体对原来袒露于外界的芯片、器件以及连接线路进行支撑、保护,担保了芯片利用的可靠性。塑封设备的事情效率可达每小时35千个芯片。激光打标、引脚电镀、切筋成型设备紧张对塑封后的芯片进行激光打标、引脚电镀、切筋成型等处理。个中切筋成型是将已完成封装的产品成型为知足设计哀求的形状与尺寸,并从框架或基板上切筋、成型、分离成单个的具有设定功能的成品的过程。在芯片塑封后,其稳定性大幅增强,因此塑封之后对封装设备的技能哀求相对较低。

(2)前辈封装设备

对付前辈封装可以参考我们在芯片家当链系列之封装测试中的先容,前辈封装的发展可以增大封装设备需求,详细表现在:前辈封装中,芯片层数增加,芯片厚度须要更加轻薄以减小体积,因此减薄设备需求增加;Chiplet中,芯片变小且数量变多,划片时须要将晶圆切割为更多小芯片,因此划片机需求的数量和精度都会提升;芯片变小且数量提高之后,对贴片机的需求量和精度哀求都会提升。接下来我们从前辈封装工艺的角度对其所用到的设备进行大略先容。

Bumping(凸块)工艺设备,紧张运用与凸块工艺中。凸块是定向指成长于芯片表面,与芯片焊盘直接或间接相连的具有金属导电特性的突起物。根据材料,凸块可分为金凸块、铜镍金凸块、铜柱凸块、焊球凸块。凸块是芯片倒装必备工艺,是前辈封装的核心技能之一。

以金/铜凸块为例,Bumping的工艺紧张为:(1)采取溅射或其他PVD的办法在晶圆表面沉积一层Ti/Cu等金属作为电镀的种子层;(2)在晶圆表面涂一定厚度的光刻胶并光刻出所需图形;(3)对晶圆进行电镀,通过掌握电镀电流大小、电镀韶光等,从光刻胶开窗图形底部成长并得到一定厚度的金属层;(4)去除多余光刻胶。锡凸块工艺与铜凸块流程相似,其构造紧张由铜焊盘和锡帽构成(一样平常合营再钝化和 RDL 层),差别紧张在于焊盘的高度较低,同时锡帽合金是成品锡球通过钢板印刷,在助焊剂以及氮气环境下高温熔融回流与铜焊盘形成的整体产物。铜镍金凸块工艺采取晶圆凸块的基本制造流程,电镀厚度超过10μm。新凸块替代了芯片的部分线路构造,优化了I/O设计,大幅降落了导通电阻。

知道了凸块的工艺流程,就可以创造在其工序中用到光刻机等多种前道设备,可以参考我们对前道设备的先容,在此不再赘述。除了这些前道设备外,凸块紧张用到的前辈封装设备为倒装机、植球机、回流炉等。倒装机即是用于倒装芯片的贴片机。植球机是在芯片上栽种焊球的设备,可以大批量的芯片植球。回流焊机也叫再流焊机或“回流炉”,它是通过供应一种加热心况,使焊锡膏受热融化从而让表面贴装元器件和PCB焊盘通过焊锡膏合金可靠地结合在一起的设备。

TSV工艺设备,紧张运用于硅通孔工艺中。TSV的制作工艺流程包括:(1)通孔刻蚀:深反应离子刻蚀(DRIE)、激光刻蚀、湿法刻蚀;(2)绝缘层、阻挡层和种子层沉积:PECVD、MOCVD、PVD;(3)通孔内导电物质添补:MOCVD添补钨、LPCVD添补多晶硅、电镀添补铜;(4)晶圆减薄:CMP;(5)叠层键合:氧化物键合、金属键合、粘合剂键合。通过工艺流程可以知道TSV工艺设备紧张用到的是刻蚀、沉积、电镀、CMP等前道设备,以及键合设备。

RDL工艺设备,紧张运用于RDL工艺中。RDL的紧张工艺包括:(1)形成钝化绝缘层并开口;(2)沉积粘附层和种子层;(3)光刻显影形成线路图案并电镀添补;(4)去除光刻胶并刻蚀粘附层和种子层;(5)重复上述步骤进行下一层的 RDL 布线。RDL须要的设备包括曝光设备、PVD设备等,也紧张是前道设备。

从市场规模来看,根据SEMI数据,2021年环球半导体封装设备市场规模为71.7亿美元,占同期环球半导体设备市场规模

的比例约为7%。个中贴片机占30%,划片机占28%,键合机约占23%,切筋与塑封设备占比18%,电镀设备在封装设备行业中占比最小,大约在1%旁边。

从竞争格局来看,环球封装设备呈现寡头垄断格局,ASM Pacific、K&S、Besi、Disco、Towa、Yamada等公司霸占了绝大部分的封装设备市场,行业高度集中。ASM Pacific产品覆盖面最广,环球市场霸占率达22.5%,为封装装备龙头。Disco在半导体封装领域紧张涉及减薄机、划片机及切筋成型设备,是后道工艺中减薄机及划片机领域的细分龙头,据 SEMI,2020年Disco 在划片机及减薄机中的市占率分别达81%、73%。Besi紧张产品为贴片机、塑封机等设备,产品谱系较广;K&S的上风设备紧张为键合机。

2、测试设备:我们已经知道半导体检测根据利用的环节以及检测项目的不同,可分为前道检测和后道检测。半导体测试环节是避免“十倍本钱”的关键。所谓“十倍本钱”是指芯片故障若未在测试环节中创造,那么在后续电路板级别中创造故障导致的本钱将在十倍以上。本文所说的测试设备即为后道测试设备,按照封装前后分为晶圆检测( CP)和成品检测( FT),紧张系功能和电参数性能的检测,属于半导系统编制造后道检测,紧张测试设备为测试机、探针台、分选机。 CP测试紧张用到测试机、探针机;FT测试紧张用到测试机、分选机。

注:我们之前已经讲过芯片的三种测试:WAT、CP和FT。在此再补充一下流程信息:晶圆代工厂制造完成的晶圆在出厂前会经由一道电性测试,称为WAT。WAT通过的晶圆被送去封测厂,封测厂首先进行CP测试,完成后进入封装环节。封装完成后的产品再进行FT测试,通过的产品才能对外出货。因此一样平常情形下,WAT是在晶圆厂完成的,CP和FT则都是在封装厂完成的。此外,过程掌握测试为晶圆制造全过程的检测,紧张用到光学显微镜、毛病不雅观测设备等;设计验证测试由于为对芯片样片的全流程检测,我们在之前的篇章中已经进行过先容。

CP测试通过探针台和测试机合营利用,测试过程紧张为:探针台将晶圆逐片传送至测试位置,芯片端点通过探针、专用连接线与测试机的功能模块进行连接,测试机对芯片施加输入旗子暗记并采集输出旗子暗记,以判断芯片功能和性能是否达到设计规范哀求。对裸片的测试结果通过通信接口传送至探针台,探针台会根据相应的信息对芯片进行打点标记,形成晶圆的Mapping,即晶圆的电性能测试结果。CP测试设备紧张由支架、测试机、探针台、探针卡等部件组成。CP测试会统计出晶圆上的芯片合格率、不合格芯片的确切位置和各种形式的良率等,可用于辅导芯片设计和晶圆制造的工艺改进。

FT测试通过分选机和测试机合营利用,测试过程紧张为:分选机将被测芯片逐个传送至测试工位,被测芯片的引脚通过测试工位上的基座、专用连接线与测试机的功能模块进行连接,测试机对芯片施加输入旗子暗记并采集输出旗子暗记,判断芯片功能和性能是否达到设计规范哀求。测试结果通过通信接口传送至分选机,分选机据此对被测芯片进行标记、分选、收料或编带。FT测试系统常日由支架、测试机、分选机、测试板和测试座组成。FT测试环节的数据可以用于辅导封装环节的工艺改进。

CP测试和FT测试在确保芯片良率、掌握生产本钱、辅导IC设计和生产工艺改进等方面都起到了至关主要的浸染。对付两者的差异我们简述如下,CP的紧张目的在于挑出坏的裸片,减少后续的封装和FT测试本钱;FT的紧张目的确保芯片符合交付哀求,避免将不合格的芯片交付给下贱用户。比较于FT,CP的技能哀求更高,难度更大。芯片封装后处于良好的保护状态,体积也较晶圆状态的裸片增加几倍至数十倍,因此FT对清洁等级和作业风雅程度的哀求较CP低一个级别,但测试作业的事情量和职员用工量更大。接下来我们对测试设备进行逐一先容。

(1)测试机:是检测芯片功能和性能的专用设备,其利用贯穿于设计验证、CP和FT。测试机对芯片施加输入旗子暗记,采集被检测芯片的输出旗子暗记与预期值进行比较,判断芯片在不同事情条件下功能和性能的有效性。

按照测试机所测试的芯片种类不同,测试机可以分为仿照/数模稠浊类测试机、SoC测试机及存储器测试机等。仿照类测试机紧张针对以仿照旗子暗记电路为主、数字旗子暗记为辅的半导体而设计的自动测试系统;SoC测试机紧张针对SoC芯片即系统级芯片设计的测试系统;存储测试机紧张针对存储器进行测试,一样平常通过写入一些数据之后在进行读回、校验进行测试。 存储、SoC测试机技能难度相对较大。

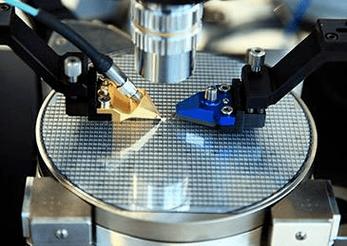

(2)探针台:卖力晶圆运送与定位,使晶粒依次与探针打仗完成测试。探针台紧张供应wafer的自动高下片、找中央、对准、定位以及按照设置的步距移动wafer的功能,以使探针卡上的探针总是能对准硅片相应位置进行测试。由于探针台只涉及探针与焊盘的可靠打仗,电性测试由专用的测试机来实行,使得探针台可以通过通讯接口搭载不同的测试机,实现对各种晶圆进行针测的可能。因此,探针台成为一台在晶圆针测中可以普遍适用的通用性工艺装备。

(3)探针卡:是半导体晶圆测试中被测芯片和测试机之间的接口,被认为是测试设备的“指尖”,是晶圆测试的核心耗材。晶圆测试时,被测工具安置于探针台之上,然后用探针卡上的探针与芯片上的pad(焊垫)或Bump(凸块)直接打仗,使得测试机和芯片直接进行旗子暗记通讯,并将被测器件中的反馈旗子暗记传输回测试机,从而完成测试机对芯片的参数测试。

探针卡属于定制器件,不具备通用性,但利用寿命相对较长,因此具备设备和耗材的双重属性。每一种芯片的引脚排列、尺寸、间距变革、频率变革、测试电流、测试机台有所不同, 都须要供应商根据芯片设计公司供应的输入信息进行探针卡的定制化设计,以知足特定产品的测试需求。以是随着芯片产品型号增加、产量增长,晶圆测试需求增加,对探针卡的花费量也将大幅增长。

随着技能的迭代发展,探针卡已从悬臂式探针卡、垂直式探针卡发展进入MEMS探针卡时期。传统探针是通过对特定合金进行拉丝工艺得到的,难以得到同等性良好的微米直径级别的材料。MEMS制造技能则可制作出微米级构造的MEMS探针用于探针卡。此外,MEMS探针卡可以实现全体晶圆的同测,避免了反复测试对晶圆的侵害。MEMS探针卡凭借高密度细间距的阵列排布、知足全体晶圆同测、可测试超高频、吞吐量大、测试可靠性高档上风,逐渐成为探针卡的主流运用。

探针卡紧张由PCB、探针、MLC/MLO陶瓷基板等构成,PCB板紧张用于承载探针,为确保针距不发生较大位移,依据运用环境选用不同的材料(包括金属片、陶瓷片、环氧树脂及垂直头等),将探针固定于PCB板。探针是探针卡中代价量最大的部件,占探针卡总本钱近五成。

(4)分选机:具有承载待测品进行测试的自动化机器构造,其内有机器机构将待测品一颗颗从标准容器内自动的送到测试机台的测试头(Test Head)上接管测试,测试的结果传回分选机,而后分选机依其每颗待测品的电性测试结果来作分类(此即产品分Bin)的过程。

根据传输办法不同,半导体分选机分为平移式、转塔式、重力式、测编一体机四类型。分选机广义的终测分选流程为:上料、方向检测、电参数检测、激光打印及印字打印、2D 引脚/3D5S检测、分选和编带。普通分选机在上料后仅合营测试机进行电参数检测,完成后便开始分选和编带。测编一体机可完成上述所有流程,实际上测编一体机也可以分为重力式、平移式、转塔式等类型,由于集成功能较多,因此构造繁芜,技能壁垒较高。详细来看,重力式分选机构造大略,投资小;平移式适用范围广、测试韶光较长或前辈封装情形下上风明显;转塔式适宜体积小、重量小、测试韶光短的芯片。

从市场规模来看,据SEMI 和Frost & Sullivan 2022年预测数据显示,2023年半导体测试设备市场规模有望达70.7亿美元,同-7.3%;个中中国半导体测试设备市场规模估量为25.3亿美元,同比-3.1%,占比提升至36%。2024年市场有望迎来拐点,估量环球半导体测试设备市场规模有望达81.9 亿美元,同比+15.8%;个中中国半导体测试设备市场规模约为27.9亿美元,同比+10.3%,占环球34%。

从市场构造来看,测试设备中,测试机在CP、FT两个环节皆有运用,而分选机和探针台分别仅在设计验证和成品测试环节及晶圆检测环节与测试机合营利用,且测试机研发难度大、单机代价量更高,因此测试机代价量占比最大,达到63%占比,而分选机、探针台占比分别为17%、15%。在测试机市场空间占比中SoC、存储器、仿照/数模稠浊类、其他测试机分别为60%、21%、15%和4%。

从竞争格局来看,环球半导体后道测试设备行业高度集中,测试机市场呈泰瑞达(Teradyne)和爱德万(Advantest)双寡头垄断局势,探针台市场也呈双寡头垄断,分选机竞争格局相对分散。据SEMI数据,2020年泰瑞达、爱德万分别霸占环球测试机市场规模的约51%/40%,细分来看,泰瑞达、爱德万分别占SoC&逻辑测试机市场的约59%/37%及存储测试机市场规模的约 32%/51%。 据CSA

Research,2018年东京精密(Tokyo Seimitsu)和东京电子(Tokyo Electron)占探针台市场份额分别为约 46%/27%。 分选机方面,据前瞻家当研究院,2018年,科休、爱德万、鸿劲精密、长川科技市占率分别约为37%/12%/8%/2%。

至此我们已经通过三篇文章完成了对半导体设备的梳理,接下来我们将连续我们的旅程,开始对半导体材料的先容,让我们下次再见吧。