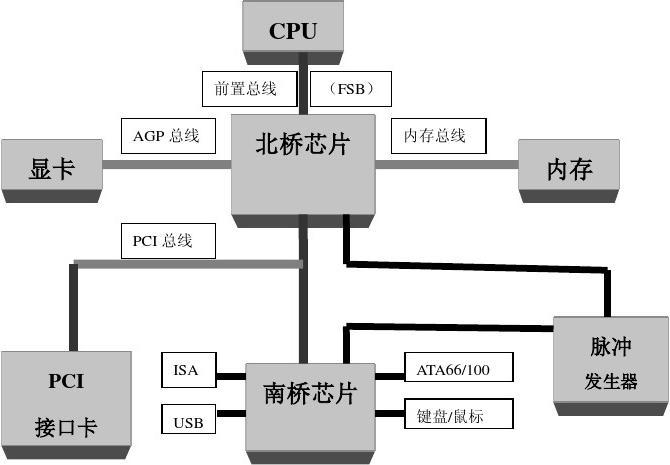

1、概述:如图一所示是全体项目的硬件事理框图:

图一

(1)ZX237520V2模块

全体项目采取复兴微电子 ZX297520 方案的核心板Core 100作为主控模块,其主频为 624MHz,装备大容量 DDR2 RAM 和高速 SPI Flash。

Core 100 核心板模块有着完善的外部运用接口,可以在 MIFI/UFI,室内型/室外型 CPE,家庭综合网关,车载路由领域运用。

其紧张外围接口为:

l USB2.0 接口,支持高速和全速模式,支持HOST 模式和Device 模式

l HSIC 接口,支持高速模式,支持HOST 和Device 模式

l 支持2 组SDIO 接口,可分别用于SDcard 和WIFI

l 支持四线制SPI 接口

l 支持四线制PCM 接口

l 支持一组四线制串口和一组两线制串口

l 支持一组SIM 卡接口

l 支持一组I2C 接口

l 支持一组RMII 接口,结合PHY 芯片可用于以太网通信

l 支持SLIC 接口,合营SPI 和PCM 接口,可用于固定电话机的运用

l 支持ADC,JTAG 调试口,休眠唤醒接口

l 2 路天线接口,支持主副天线切换功能

l 时钟输出

l 其他功能:按键开机,充电开机,复位,规复出厂设置,休眠唤醒,LED 灯掌握

个中本设计中只用到了USB接口外接其他设备;一起SDIO接口连接RTL8192ES_CG芯片以拓展WiFi功能;一起RMLL接口,连接PHY芯片IP101GR,以拓展以太网通信网络功能;一组SIM卡接口;两路天线用于收发4G移动无线数据旗子暗记;以及一些必要的IO端口用于LED灯的显示掌握。

(2)RTL8192ES_CG WIFI芯片

RTL8192ES_CG芯片支持 IEEE 802.11b/g/n,拥有两路2.4G差分WiFi发送通道,以及两路2.4G差分旗子暗记吸收通道,个中两路差分发送通道可以通过软件配置变为收发共用模式。本设计中采取了两路的2.4G差分发送通道,其他两路的差分吸收通道没有利用,芯片跟模块之间的通信采取SDIO接口。芯片有自己的1.2V_LDO可以给其内核供电,采取40M晶振为芯片供应基准频率。芯片WAKE、chip_EN 连到Core 100 GPIO 管脚,起WLAN 的唤醒、复位功能

(3)PHY芯片IP101GR

IP101GR 是单口的10/100 MLL/RMLL/TP/Fiber快速网络收发芯片,支持IEEE 802.3/802.3u标准,支持自动MDI/MDIX转换功能,支持基线洒脱补偿功能,支持中断等。本设计中采取RMLL接口与模块进行通信,以拓展模块的以太网功能。芯片采取25M晶振为内核供应基定时钟。

(4)DC-DC设计

本设计采取的DC-DC芯片为STI3470,该芯片为SOT23-6封装,尺寸小,输入电压范围4.5-16V,输出电流可达2A.设计中利用两颗该芯片,分别产生4.0V和3.3V的直流电给模块,WiFi,PHY芯片供电。

(5)其他

本设计中其他的复位,配置,LED灯显示等细节,将不才面先容。

2、 ZX237520V2模块电路事理图解释

图二

如图二所示是ZX237520V2模块的管脚接线图,个中还包括部分外围接口电路,如4G天线接口电路,串口电路,供电管脚滤波电路等。

图三

如图三所示是模块的一些配置管脚连接图,紧张包含模块的开机上电、充电办法,WPS按键,模块按键,开机boot,以及一些并未利用但是由于NC后电平不愿定可能影响模块正常事情的管脚的接线电路图。

图四

如图四是模块掌握的LED旗子暗记指示灯的电路连接图,由于模块的IO端口可能存在驱动能力不敷的问题,因此每个掌握旗子暗记灯的IO端口都通过放大其驱动能力。

图五

如图五,是模块的USB接口电路图以及SIM卡接口电路图

下面附上一张模块的IO管脚配置解释表,便于工程师们尽快理解模块的IO资源利用情形。如下表所示:

上表中有些空缺未解释的管脚均是一些电源供电管脚以及两路天线管脚等,都是一成不变的,因此表中没有表示,详细请参考对应的事理图连接。

末了模块采取的4.0V和3.3V供电均有DC-DC电路产生,同事模块自身会输出1.8V的电压,用来供应一些IO口的输出电压驱动赞助,或者是配置上拉需求。同事一个WiFi芯片和PHY芯片中将要利用1.8V的管脚供应供电电源。

3、RTL8192ES_CG芯片的外围电路连接图

图六

如图六所示,RT8912ES芯片拓展的是两路2.4G的RF线路,个中两路2.4G差分吸收线路并没有利用;在RF线路的末端增加了无源滤波器,用以滤出吸收到的滋扰旗子暗记或者是发送出去的噪声旗子暗记,用以提高收发旗子暗记的质量。每路RF线路有两个兼容天线,一个是板载天线,一个是兼容的PCB天线,默认采取板载天线以节约本钱。

下表是RT8912ES芯片的部分管脚利用解释,大家设计的时候可以参考。

表二

芯片采取40M晶振电路为内核事情供应基定时钟,采取SDIO接口与模块进行高质量的高速通信,其3.3V的供电由DC-DC芯片供应,1.8V的供电来源是模块供应的,1.2V的内核供电由芯片本身进行DC变换产生。

4、 PHY网络芯片IP101GR外围电路解释

如图七,图八所示是PHY芯片的基本配置连接图,以及芯片的管脚接线图;由图七可以看出,IP101GR芯片的地址为0001b,芯片处于经典的测试模式,以RMLLA模式与主控模块进行通信,以LED0模式进行状态指示掌握,通信电缆方面采取传统的八线同轴网线进行通信与外网通信。

图八中,展示了PHY芯片的PIN脚资源的利用情形,供电线路及滤波,晶振电路,与主控模块的通信链路,状态LED显示掌握电路,以及缺点中断电路等。

图九

如图九所示,是PHY芯片与网络滤波器之间的链路连接图,其余还包括网络滤波器与RJ45接口的线路连接状况。由图中可以看到网络变压器的中间抽头是接地的,而有些PHY芯片与之搭配的网络变压器的中央抽头则须要连接电源,因此在选用网络变压器时须要把稳。当然设计中做了兼容。

5、 供电DC-DC电路解释

图十

如图十所示:整机利用12V的DC电源进行供电,DC-DC芯片采取STI3470,该芯片的输入电压范围在4.5V到16V,因此整机的供电电压并不一定限定在12V,其他常用的9V或者5V适配器也可以利用,但须要把稳一点,DC座子进来后有一个二极管,在供电电流为1A的范围内其正引导通电压为0.6V,且随着供电电流增大,例如电流达到3A时,其最大正引导通压降可以上升到0.9V,以是若整机带重载的时候则不适宜采取5V的DC电源。芯片的输出持续输出电流可以达到2A,足可以知足设计哀求。芯片的反馈电压一样平常是0.6V,用户可以通过调度反馈电阻的参数来设置输出电压。

本设计中产生的3.3V电压用于供应模块,WiFi芯片以及PHY芯片利用,4.0V用于供应模块用电。